FPGA-Powered

AV Processing

FPGA-Based Video/Audio Processing with Predictable Latency

Build real-time video and audio systems with predictable timing, even at peak load. FPGA-based processing avoids the instability of software pipelines and keeps video and audio in sync for broadcast, ProAV, and telecom products where timing issues matter.

Promwad delivers end-to-end FPGA video and audio solutions ready for production. We handle interoperability with ST 2110, NMOS, AES67, and IPMX, and guide projects from system design to production delivery with clear expectations on timing and scope.

Need LatencyReview?

Our Partners and Companies Employing Promwad Solutions

The Real Challenge: Consistency Under Load

Problem: In live video and audio systems, issues usually come not from “high latency,” but from latency changing unpredictably. CPU/GPU and software-based pipelines can behave differently under load, updates, or parallel tasks, leading to sync issues, unstable timing, and risks that are hard to plan for.

Promise: Our approach focuses on predictable, fixed timing using FPGA-based processing for Full HD/UHD/HDR or up to 8K workflows. By designing data paths with defined limits and stable behavior, independent of operating systems, we help teams deliver systems that behave consistently in real deployments.

Why Promwad

Promwad “plugs in” as your engineering partner at any stage — rescue, migration, or scaling — and can own delivery end-to-end, including RTL/logic, firmware, drivers, and verification.

What engineers and product leaders value:

Scale & impact:

We also integrate into your existing vendor ecosystem:

Planning or upgrading your FPGA video/audio pipeline?

Start with a latency & interoperability check

What We Build: Service Scope & Deliverables

We build FPGA video processing and FPGA audio processing solutions that hit tight timing budgets — including deterministic latency codecs and DSP blocks.

Core deliverables

- FPGA logic design (RTL/IP integration) for processing + transport

- Embedded firmware and platform features: secure boot, configuration management, and control-plane integration

- Host-side enablement where needed (drivers, interfaces, tooling)

- Verification assets: latency/sync tests, regression hooks, documentation for production readiness

Custom FPGA IP cores for audio

- SRC/resampling, channel mapping, de-embed/embed

- Mixers, conditioning, routing logic (high channel density paths)

Custom FPGA IP cores for video

- Scaling, color space conversion, HDR paths

- Frame/line buffering (latency-controlled), mixers, multiview

- Sync blocks and timing alignment

Commercial IP integration (when it accelerates time-to-market)

- Codec/processing blocks + AV-over-IP compliance components

- Standards ecosystems: ST 2110 / NMOS / AES67 / IPMX

Tell us your formats and latency goals — we’ll define the next step

Vadim Shilov, Head of Broadcasting & Telecom at Promwad

Standards-First FPGA Integration

You don’t just need processing blocks — you need interoperability in mixed-vendor environments.

Common standards we support around low-latency pipelines:

- SMPTE ST 2110 + NMOS, and timing/networking foundations like PTP (IEEE 1588), QoS, IGMP (when transport & sync are in scope)

- AES67 for AoIP interoperability (and coexistence with other AoIP ecosystems when required)

- IPMX for ProAV-oriented AV-over-IP designs (built on ST 2110 building blocks, with NMOS/AES67/PTP in the stack)

Latency engineering techniques we apply:

- Deterministic buffering strategies and pipeline-depth control - Clock-domain handling and sync alignment - Lip-sync validation and failover testing across realistic conditions

Application Areas

Where deterministic latency matters most:

Live production

mixers, multiview, sync, cross-bridges, ultra-low-latency interfaces

UHD/HDR FPGA pipelines

performance paths for Full HD, UHD, HDR processing/transcoding

Embedded edge devices

FPGA-based decode/encode + display/output paths for panels and viewfinders

AoIP endpoints/routers

SRC, high channel density, routing, timing alignment

Studio gateways & hybrid SDI/IP devices

migration without chaos

From Variable Software Latency to Deterministic FPGA Datapaths

A typical engagement looks like this:

Our Case Studies

FPGA & Hardware Projects

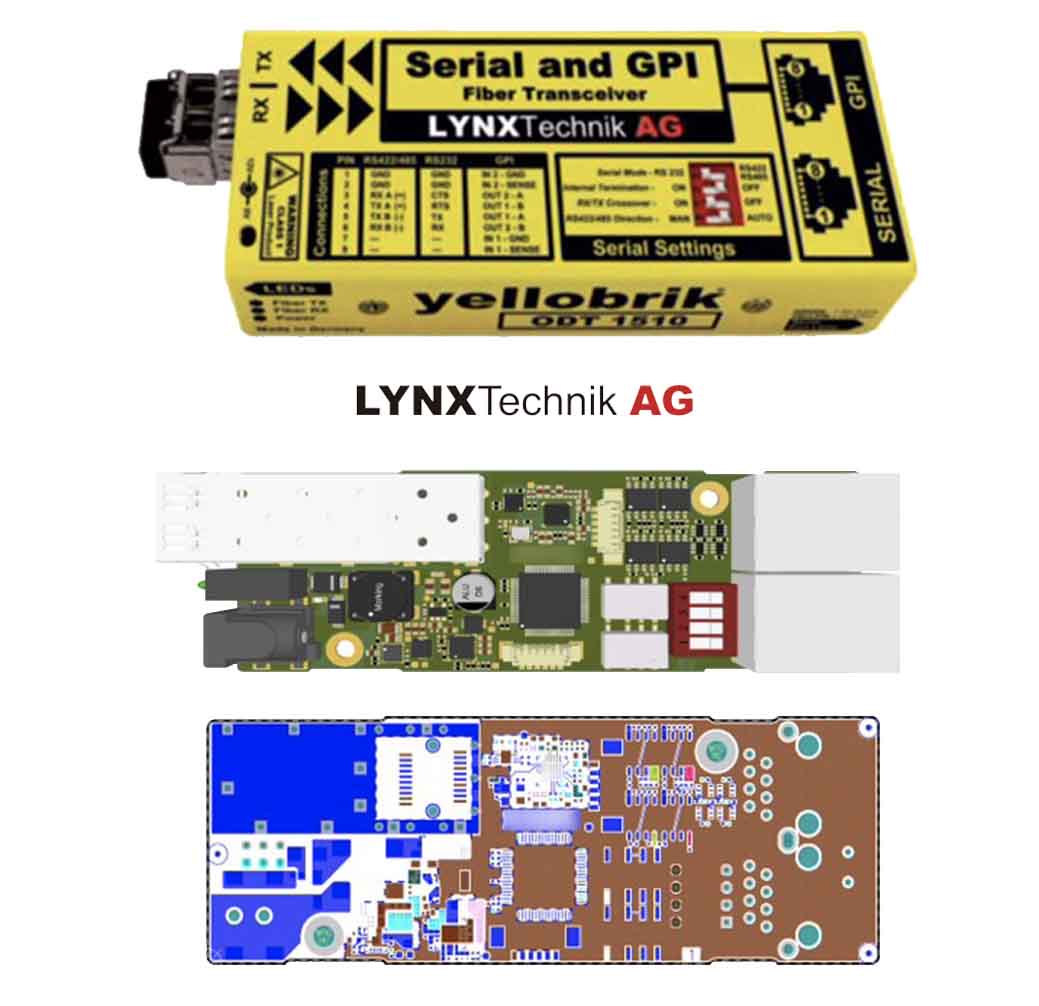

Firmware for Serial & GPI Fibre Transceiver

Pain

Solution

Result

Read the Fibre Transceiver Case

Bi-directional Quad Link 2SI/SQD Development

Pain

Solution

Result

Read the 3G/12G SDI Gearbox Case

Photo for illustration purposes only

Dedicated Team for Live-Production Device

Pain

Solution

Result

How We Ensure Quality

Delivery process built for broadcast realities: latency budgets, sync, and interoperability must be verified early.

QA specifics for live and mixed-vendor environments:

Our Engagement Models

Time & Material

– Payments for actual hours worked

– Regular reporting of time and results

– Regular communication with the team

– Connecting / disconnecting engineers on request

– Flexible development process

Dedicated Team

– Fixed monthly costs

– Custom-built team with specific competencies

– Fully dedicated engineering team

– Comprehensive IT infrastructure

– Max efficiency for complex projects

Project-Based

– Budget control

– Reduced risk

– Flexible resource allocation

– Clear scope

– Predictable timeline

– Quality control

Ready to build a deterministic FPGA video/audio pipeline — without latency or interoperability surprises?

You’ll get actionable engineering feedback and a clear next step.

FAQ

How do you guarantee predictable FPGA codec latency (vs CPU/GPU)?

What’s typical end-to-end latency, and what drives it?

Do you build custom IP cores or integrate commercial blocks? How do you validate them?

Can you integrate an ST 2110 FPGA encoder / NMOS / AES67 FPGA / IPMX FPGA stack?

Do you deliver production-ready artifacts beyond the RTL?

Can you start from existing RTL or a vendor reference design and take it to production?