ASIC Frontend Development

Verification and Prototyping Services for Custom ASIC Design

Promwad will help you develop a custom ASIC by taking care of validation and prototyping after the logical implementation of your application-specific integrated circuit.

If you're seeking a contractor for circuit verification, testing, or driver development services for your ASIC solutions, you're in the right place. Our qualified team has extensive experience in ASIC development.

Our Services

Here are the engineering services we offer to ASIC design companies and other clients on their journey to new mass-produced ASICs:

- ASIC designs modelling and simulation with HDL

- Hardware simulation and verification on Zebu, HAPS or custom FPGA development kits

- Testing with CPUs (i.e. RISC-V)

- Virtual and hybrid circuit emulation (based on Zebu & HAPS)

- Hardware and software validation

- Software-based verification (ANSI C)

- Pre- and post-silicon validation

- Custom divers development

- UVM-based pre-silicon testing

But our engineering support doesn't stop there. We can integrate your custom ASIC design solutions into specific devices and embedded systems with our Embedded Linux development services or Edge AI development.

Featured Case Study: Custom ASIC and FPGA Design

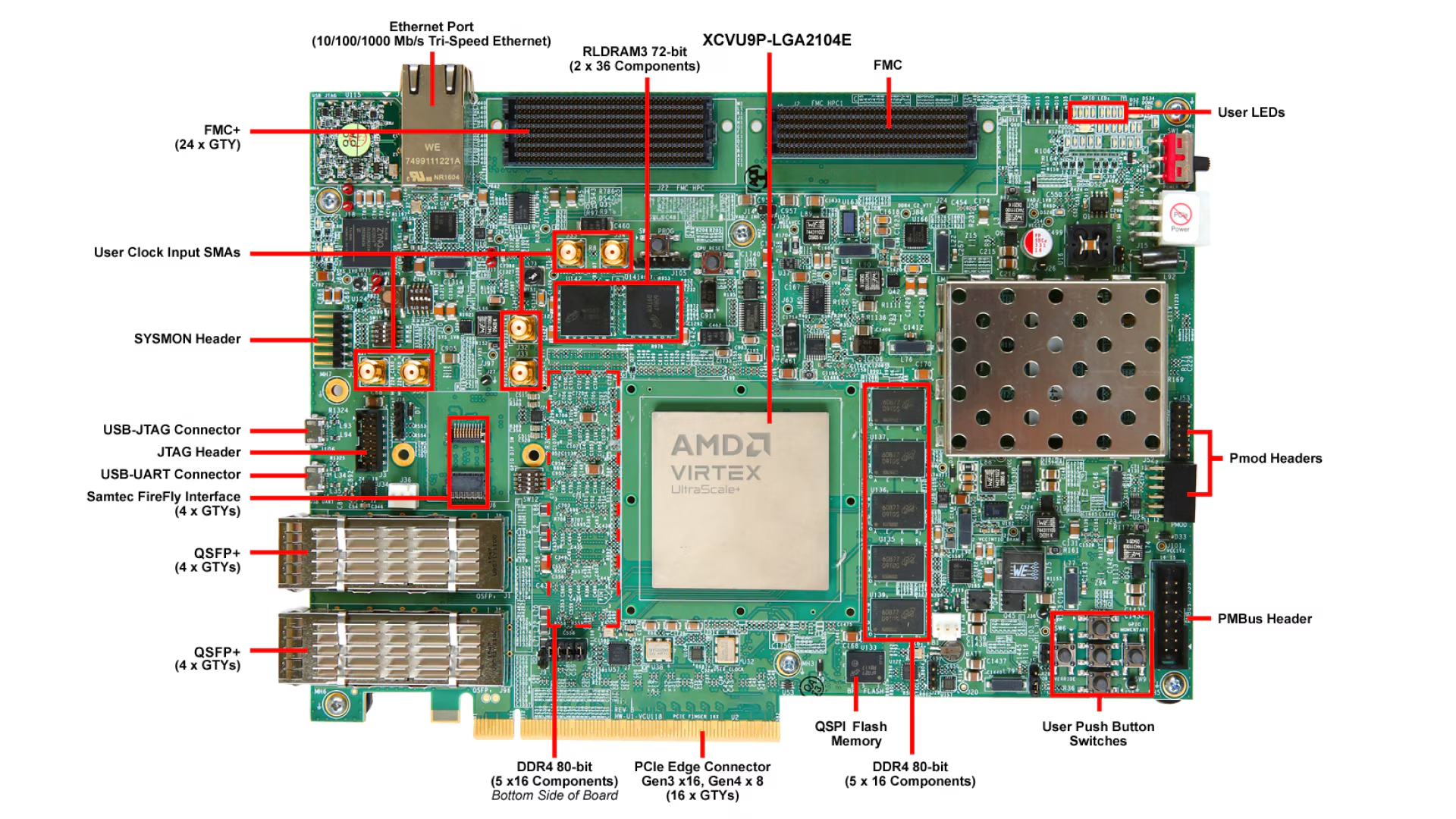

HAPS-80 Prototyping Solution by Synopsys

The project involved testing and firmware design services for custom RISC-V-based circuits.

Our team was involved in the following activities:

-

BSP and bare-metal drivers for RISC-V CPU development

-

Zero-stage and first-stage bootloaders

-

Windows driver for PCIe end-point device development (Jungo framework)

-

Implementing bring-up tests for all SoC components with communication over the QSPI bridge

-

Simulation on ZeBu

-

Emulation on HAPS-80

Our team took part in deploying the concerned RTL design on the AMD Virtex™ UltraScale+™ platform and interfacing with PHYs (AMD transceivers and external PHYs). We interfaced the following blocks designed by Synopsys:

-

PCIe root complex

-

10G MAC and 10G PCS

-

USB 3.0

The prototyping was implemented on VCU118 and HTG-960 evaluation kits with corresponding mezzanine cards. The simulation was launched on Vivado™ and VCS.

Virtex UltraScale+ FPGA VCU118 Evaluation Kit

The Peripheral Components of the Designed ASIC

PCIe end-point, AXI-DMA, GPIO, LPDDR4, UART

QSPI bridge

RISC-V

Watchdog timer, PVT sensor

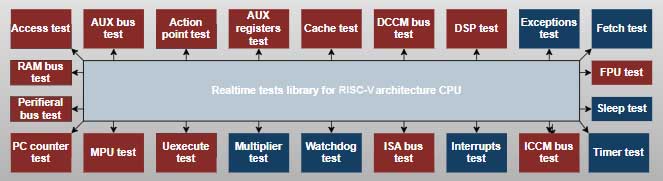

Micro Case Study on ASIC Verification

Unpredictable impact deterministic detecting on CPU and parts

Tags: RISC-V, Test, Real-time deterministic

We designed and developed a real-time CPU internal test library. The test included internal and peripheral buses, internal CPU blocks, and more. The main idea is to immediately (deterministic time) detect any faults caused by any impact, including electromagnetic pulse.

We boost your circuit development by implementing C/ASM verification software for IP blocks on Zebu, HAPS or other FPGA prototyping systems.

Our technology stack includes but is not limited to, PCIe end-point, AXI-DMA, LPDDR4, QSPI, and RISC-V (SiFive).

Are you interested in ASIC verification and prototyping?

Drop us a line about your project! We will contact you today or the next business day. All submitted information will be kept confidential.