FPGA Design

Get Custom FPGA Design Services

- Comprehensive evaluation: we assess every aspect of your project to provide valuable insights and explore opportunities.

- End-to-end design, including IP core integration, data processing algorithm implementation, and interface controller and processor core development.

- 20 years of experience delivering a wide range of high-quality FPGA/MPSoC/RFSoC firmware solutions for clients worldwide.

Andrei Smirnov, Head of the Adaptive Computing Systems Unit at Promwad

Discover Our Comprehensive FPGA Design Services

Lack of resources for FPGA development?

We guide you from idea to final product

Hardware Development

Hardware design services, including carrier boards, SoM FPGA, prototyping, and turnkey solutions.

Read more

FPGA Design& Simulation

Complete process of FPGA design and simulation, from initial concept to final implementation.

DSP & IP Core

Development

DSP algorithm design and custom IP core development to enhance system functionality and efficiency.

MCU firmware

Hardware and firmware solutions for microcontroller units (MCUs), using RISC-V, MicroBlaze and more.

Read more

Embedded Software

& BSP

End-to-end embedded software development services, including BSP for Linux and PetaLinux.

Verification

Comprehensive verification services to ensure the accuracy, reliability, and functionality of hardware and software.

Benefit From Our Services

Functional safety support

We offer expertise in functional safety standards and methodologies, using verification and validation techniques to ensure that your FPGA design meets all safety requirements.

Reduced project

cost

Our FPGA design solutions streamline processes, optimise resource allocation, and minimise overheads, resulting in reduced hardware costs and improved performance.

Diverse project

scope

We undertake FPGA projects of varying scales and domains, from catering to small businesses to enhancing urban environments through smart city solutions.

Domains We Serve

Networking

Automotive

Space

& Robotics

Video Streaming

& AI

Partnerships with the World Leading Vendors

We maintain close relationships with the leading FPGA vendors to access the latest technologies and provide you with the best solutions for your project.

Explore Our FPGA Project Expertise

As a FPGA design company, we perform the following activities:

- Specifications development.

- Architecture definition, selection of IP cores, including UFS IP cores.

- RTL descriptions development in VHDL/Verilog.

- DSP cores in Matlab Simulink (DSP – Digital signal processing).

- HLS — High-Level Synthesis. Logical and physical synthesis.

- Adaptation of IP cores to various FPGA families.

- FPGA based on AI-powered technologies.

Our Case Studies

FPGA solutions for multimedia broadcasting systems

Our team develops custom FPGA solutions for the demanding needs of multimedia broadcasting applications.

We integrate various features, including video and audio capture, processing, encoding, transmission, and display.

Discover real-world examples of our FPGA expertise in multimedia broadcasting.

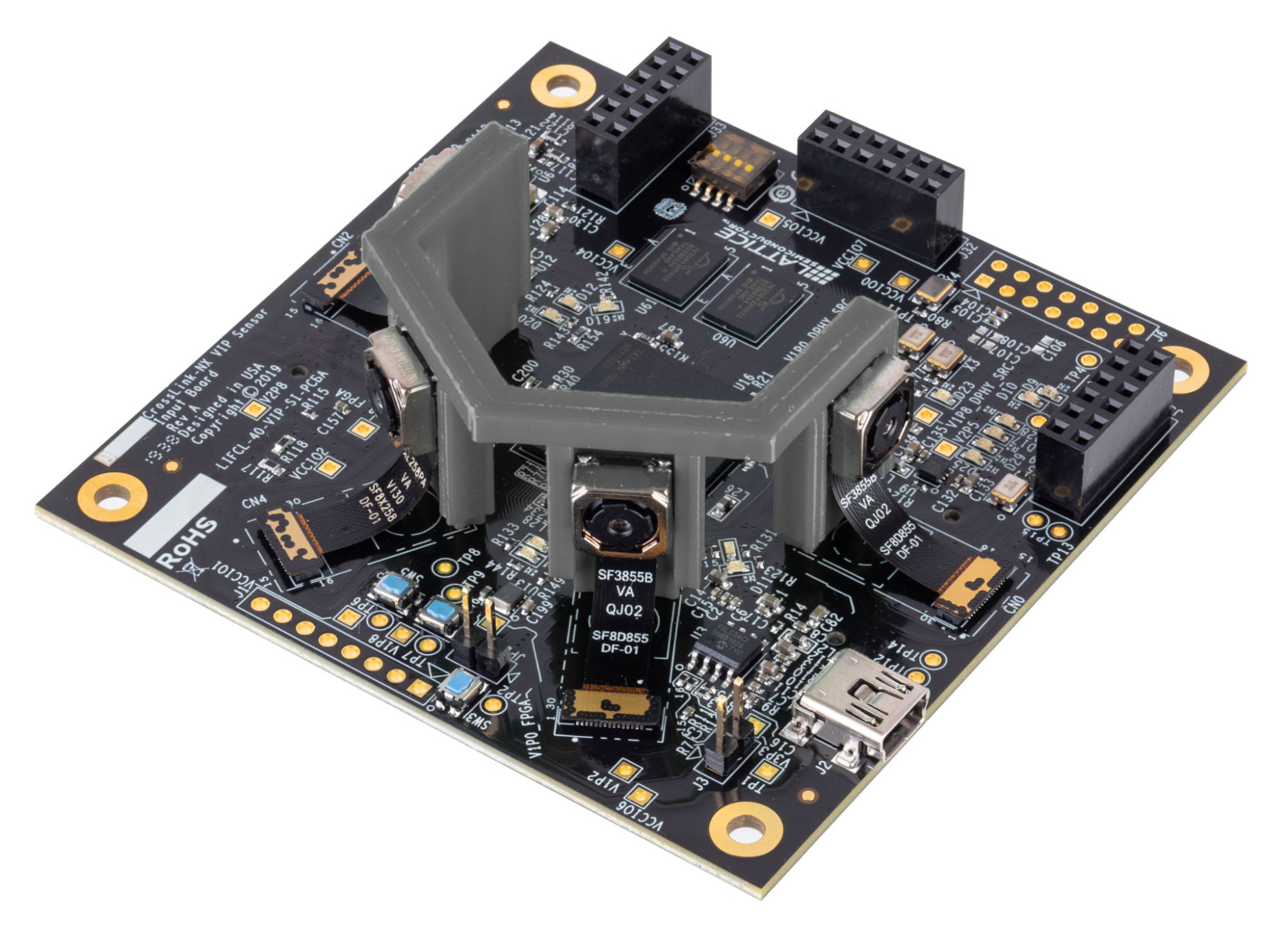

360-view camera system for trucks

We upgraded a surround-view camera system for large vehicles by developing software and replacing obsolete components.

We utilised a Lattice Crosslink-NX FPGA and NXP S32K228 microcontroller, ensuring compatibility with modern interfaces and meeting the stringent ASPICE CL2 and ASIL-B safety standards for automotive applications.

This upgrade delivered a compliant vision system, empowering the client with full technical assistance from Lattice.

LiDAR-camera fusion assistance systems for crane operators

We developed a prototype LiDAR-camera fusion system to enhance crane operation efficiency, accuracy, and safety.

This AI-powered solution combines LiDAR's precise distance measurement with camera visuals to provide real-time obstacle detection, collision avoidance alerts, and virtual overlays for improved situational awareness.

The system also offers data-driven insights for performance analysis and workflow optimisation, ultimately leading to lower costs and a significant increase in crane safety.

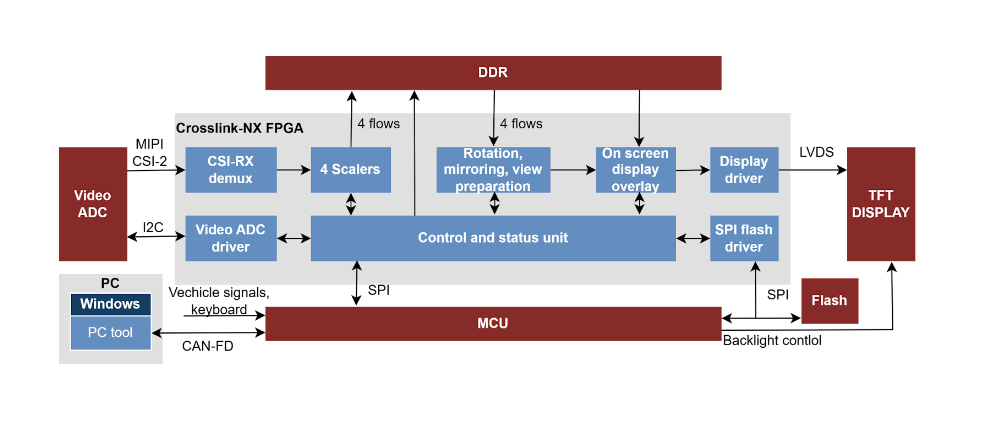

Spherical camera systems

Promwad designed a 360° camera monitoring system integrating four PAL/NTSC cameras. Each stream can be scaled, rotated, mirrored, and overlaid with markings.

Users can enable night mode with automatic illumination and adjust video parameters per stream. All configurations are saved for easy recall.

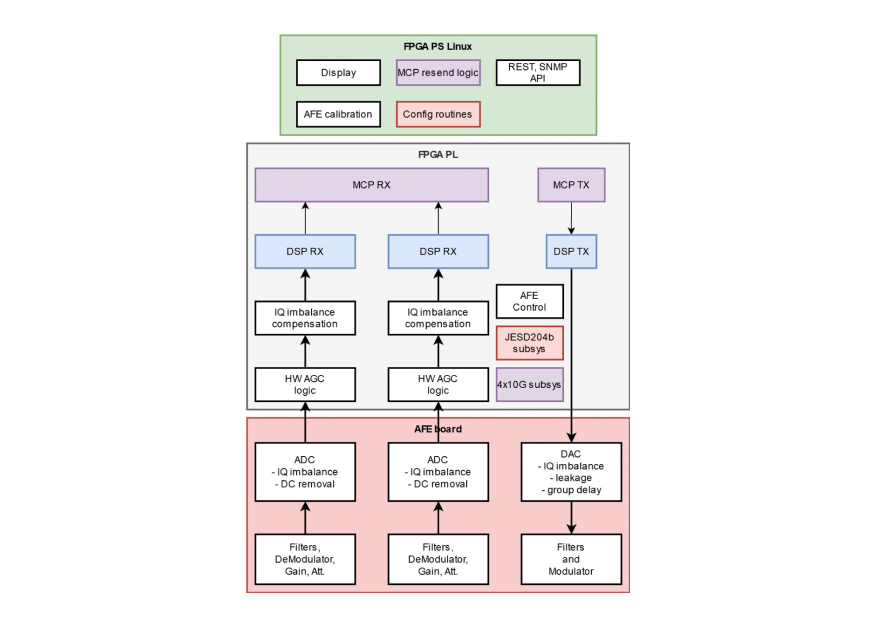

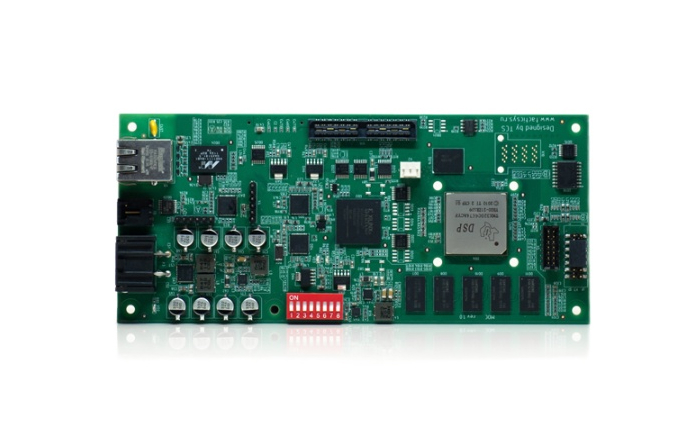

DSP module for wireless communication systems

We created a versatile FPGA module for digital signal processing (DSP) with an open architecture for wireless communication systems based on the SDR technology. The main board was based on TMS320C6674, a 4-core processor by Texas Instruments (1.25 GHz).

The modular design includes dedicated modules for digital signal processing, signal conversion, and RF communication with a wide frequency range.

Broadband software-defined radio satellite modem design

We designed a hardware and software platform for a satellite modem. This compact and scalable solution features a Zynq Ultrascale+ platform and a custom-developed frontend using high-speed converters and modulators/demodulators.

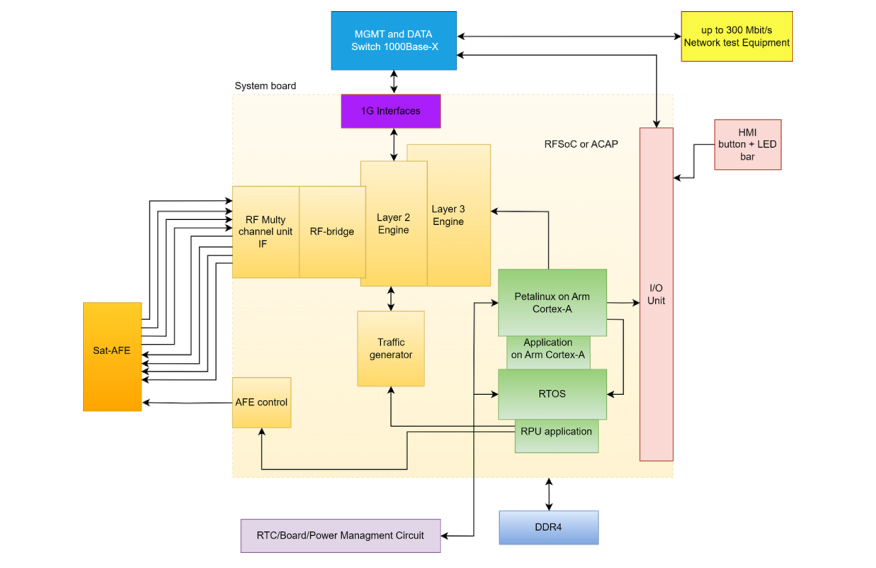

PE-3224.Satmodem

We designed and developed a next-generation satellite modem to support various network configurations and advanced functionalities.

The solution offers network flexibility (star, mesh, etc.), multi-beam capability, advanced waveforms (DVB-S2(x), MF-TDMA), high data rates (40 Mbps/connection, 160 Mbps network), and bridge/routing modes.

The Zynq UltraScale+ RFSoC platform provides a powerful and flexible foundation.

SDR modem for satellite communication

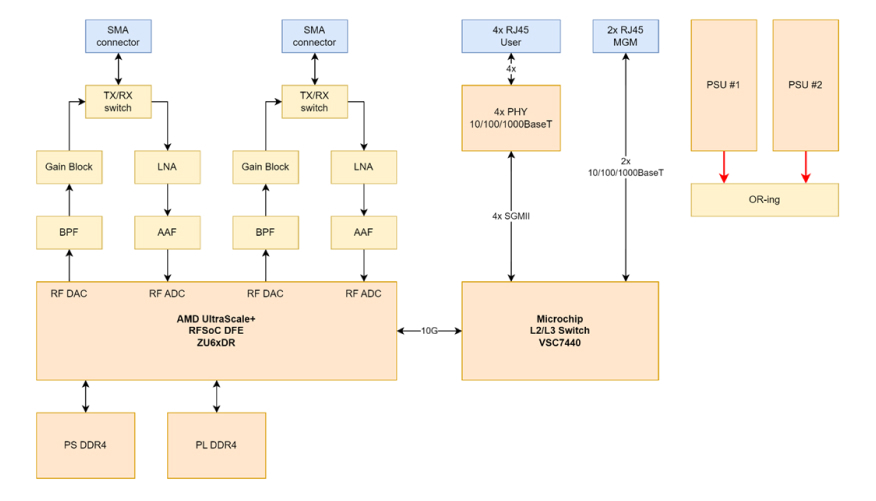

A high-performance Software-Defined Radio (SDR) modem for satellite communication. The Zynq UltraScale+ RFSoC based modem leverages a powerful DFE from AMD for efficient signal processing.

The modular design features a customisable analog front-end with LNAs, gain blocks, and filters, and supports up to 8 Gigabit Ethernet ports with optional 10G SFP+ connectivity. Redundant power supplies ensure reliable operation in critical communication applications.

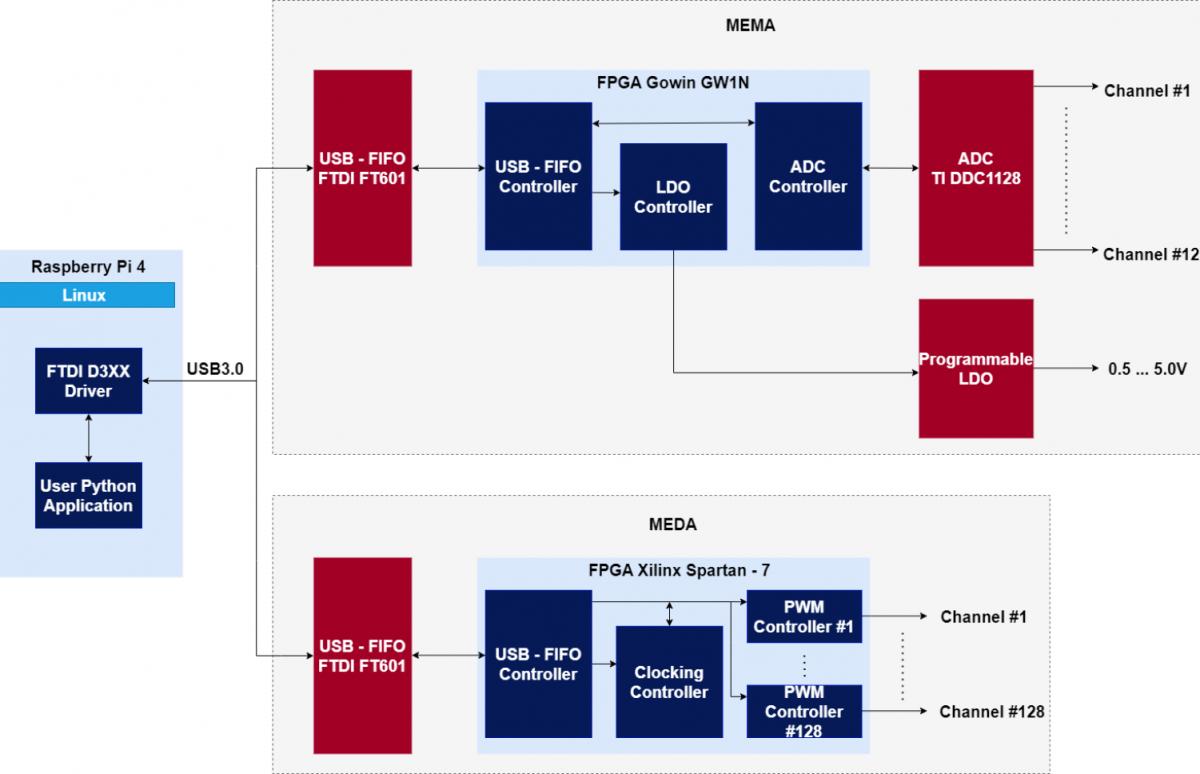

Multi-electronic driver array and multi-electronic monitor array

We developed the FPGA multichannel driver for an advanced photonic system. The unit is programmed to control the electrical power for driving and acquire and digitise data from a 500-optocoupler array connected to the programmable photonic integrated circuit.

The unit reads the optical power monitors of the programmable photonic integrated circuit, closing the control loop. These monitors provide the information to compare the actual output with the expected one and update the array control signals.

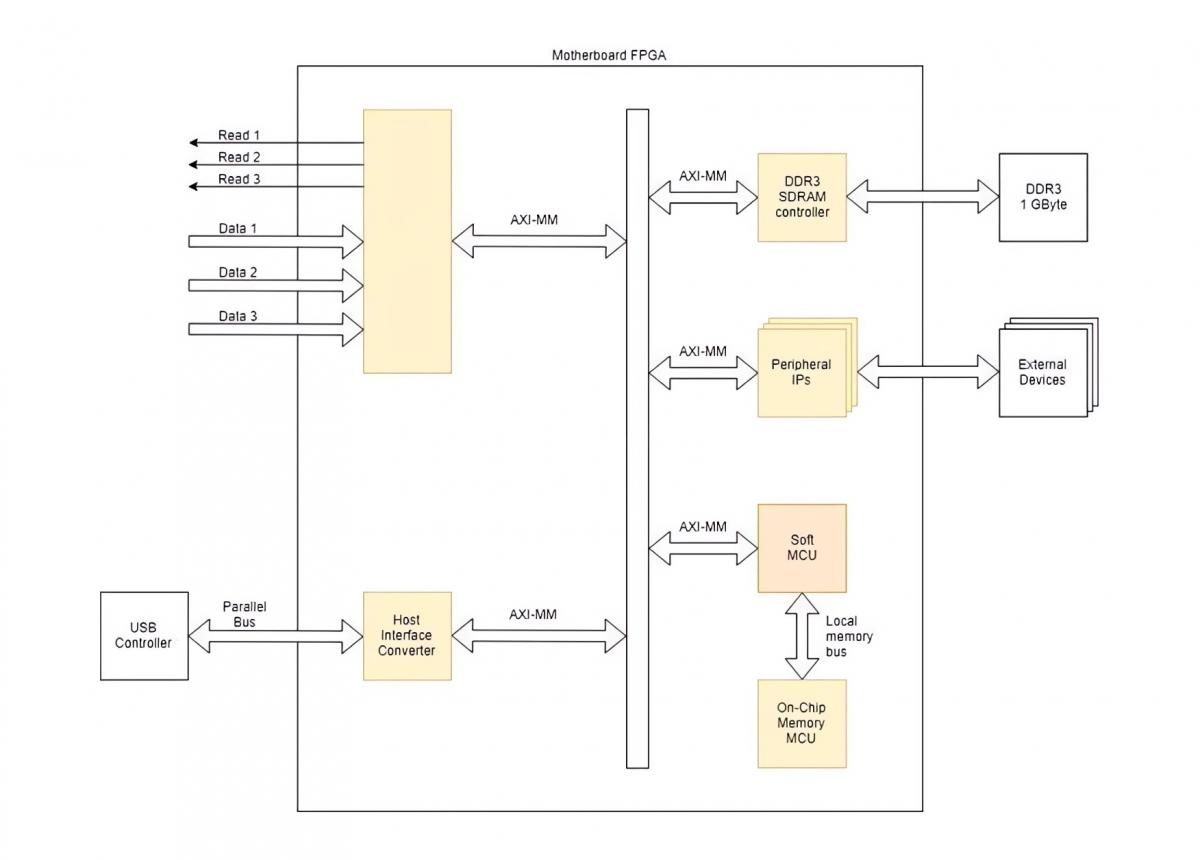

Difraction-based X-ray processing device design

We designed a high-performance X-ray processing device for explosive material detection. This system uses multiple Single Boards with ASICs and FPGAs for data acquisition and processing.

The mother board collects data and interfaces with a host computer. A custom enclosure with forced air cooling ensures optimal thermal performance for reliable operation.

Controller for IR laser

Challenge: Ensure efficient light energy delivery to achieve high productivity and minimise structural damage from heating.

Solution: Our team developed an electronic controller for a nanosecond IR laser used in cutting and drilling metal or ceramic. It features high precision and stability of pulse waveform using loop-back control, with a waveform analyser providing correction data to a waveform generator.

Software: HMI for status indication and manual control, PROFINET interface for industrial network integration. The device controls the power supply, LED pump, acousto-optic Q-switch driver, and fan system, optimising the laser pulse profile and repetition rate.

Hardware: AMD FPGA UltraScale+ MPSoC integrated with an Analog Devices AD mixed-signal front-end chip (ADC & DAC).

Software development for ADC signal buffer/transmitter

This firmware comprised several key components:

- FMC231 with ADC configuration and data acquisition.

- MicroBlaze soft processor core.

- UART IP.

- DDR3 Memory Interface (MIG).

- AXI4S-to-AXIS conversion module.

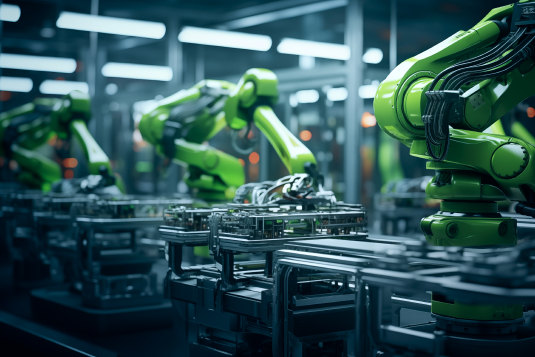

FPGA solutions for industrial automation & robotics

We develop custom industrial-standard FPGA solutions for a wide range of applications, including robotics, energy sector automation, and industrial control systems.

Our FPGA solutions are built to meet the rigorous standards required for industrial environments, ensuring reliability and long-term operation.

Learn more about our industrial FPGA solutions.

More of Our Completed FPGA Design Projects

Our Tech Map

Vitis/Vivado, Quartus Prime, Diamond, Libero, Matlab

NVidia Jetson, Alveo, OpenVINO, TensorFlow, Keras, Caffe

Verilog, VHDL, VivadoHLS, Simulink/HDL Coder, С/C++, Python

High-speed PCBs, DDR4, JESD204b, HDMI, SDI, SI, PI, Thermo modeling

Zynq UltraScale+, RFSoC, Cyclone10, ECP5, MPF500

AD9361, AD9371, ADRV9009, Radars, Custom AFE, Antenas

DPDK, UDP 10G, TCP 10G, TAPs, L1/L2 IP cores

1G, 10G, 25G/40G, 100G

How We Work With You

"In case you are planning a project in complex data processing or high-speed throughput it’s the best way to choose FPGA programming. Our experts are ready to provide top-notch hardware design & firmware development services. Moreover, we are ready to give a hand with PCB & schematic design – our experts have strong experience preparing projects of any complexity to mass manufacturing."

— Alex Krainov, CTO at Promwad

Drop us a line about your FPGA design project and get a quote!

We will contact you today or the next business day. All submitted information will be kept confidential.

FAQ

Where does the work begin? Do you sign an NDA first?

First, we sign an NDA (non-disclosure agreement) and clarify the details of the project. Then we draft a business proposal. Once the agreement is signed, our engineers get to work and you can watch your idea come to life!

What is the completion time?

What will I receive upon project completion?

Once the project reaches its conclusion, you will obtain a fully operational device, prototype, or software along with comprehensive technical documentation, source codes, and PCB design files in a CAD format. Detailed instructions on product usage will be provided to you. Additionally, we offer training sessions as needed.

How are intellectual property rights handled?

Throughout our collaboration, we ensure clear agreements are in place to address ownership and protection of intellectual property. Our standard practice includes signing NDAs to safeguard sensitive information and outlining ownership rights in project contracts. In addition, we will only mention your project on our website and other platforms with your permission.