UFS IP Core

Ready-to-Use UFS IP Core for Universal High-Performance Storage Interface

It provides a universal storage interface for both embedded and removable flash memory, making it an ideal solution for applications that require high- performance and low power consumption. UFS flash IP is based on the MIPI M-PHY physical layer standard and uses MIPI Unipro as a link layer.

Technologies UFS IP Supports

- JEDEC UFS 2.1

- M-PHY version 3.0 type-1

- UniPro standard version 1.6

- PWM Gear-1 x 2-lane

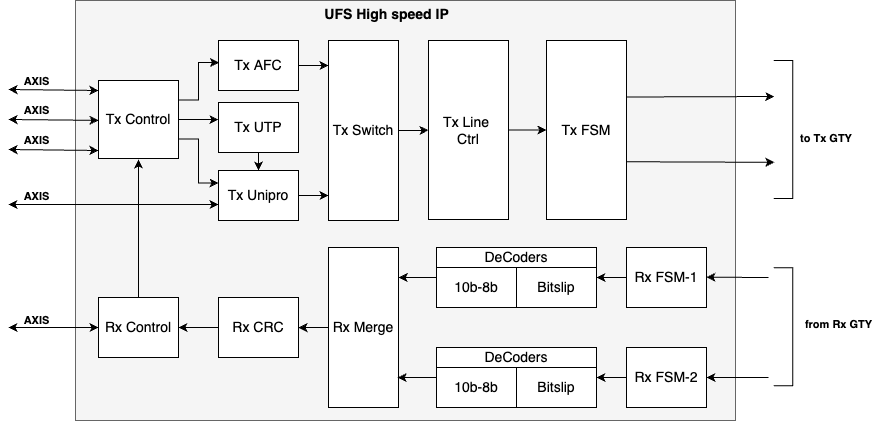

- HS-Gear-1, HS-Gear-2, HS-Gear-3 x 2-lane via GTY

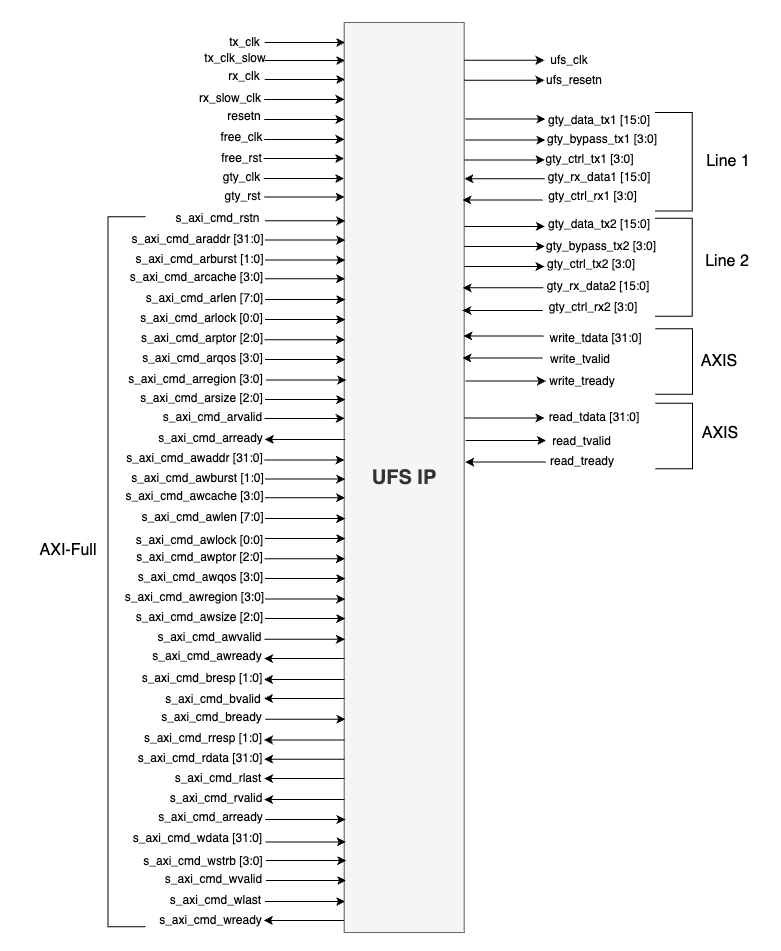

- AXI-Full and AXS interfaces

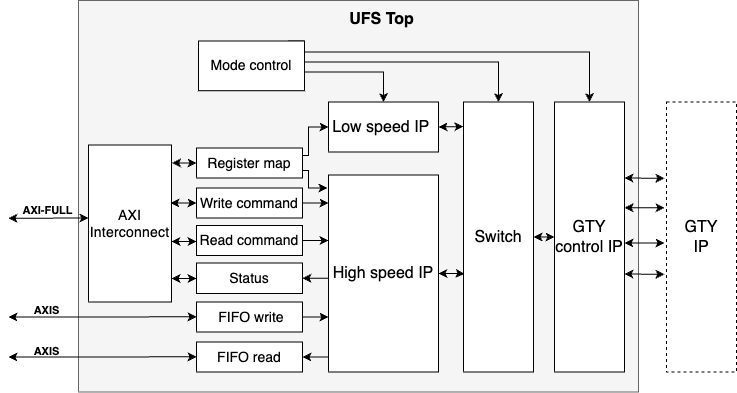

Modules of the UFS IP via GTY

- UFS low-speed and high-speed IP

- GTY control IP

- Mode control

- Switch

- Write command FIFO

- Read command FIFO

- FIFO write data

- FIFO read data

- Status FIFO

- Register map

UFS IP core via GTY structure diagram

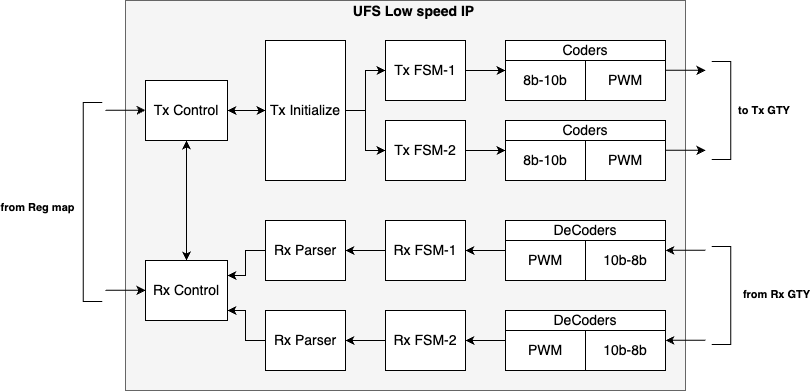

UFS low-speed IP structure diagram

How We Integrate UFS IP Core Solutions into Our Clients’ Projects

Enhancing Automotive Infotainment System

Сommissioned by a car manufacturer, our engineers improved its existing infotainment system with the UFS IP core development. The performance increased significantly, with higher data rates, resulting in faster applications and smoother navigation.

We provided the solution optimised for automotive applications and integrated it into the hardware architecture of the infotainment system. The increased speed allowed real-time data processing from various sources, including GPS navigation, multimedia streams and vehicle sensors. It enabled advanced features such as real-time traffic updates, predictive maintenance and adaptive cruise control.

Advancing Surveillance Cameras

We were tasked to improve the performance and reliability of video surveillance cameras for commercial and residential applications. The cameras are required to efficiently capture and store high-resolution video data while providing uninterrupted real-time streaming, even in challenging environmental conditions.

Our engineers integrated UFS IP cores into the cameras, ensuring compliance with industry standards. Using universal flash storage, the surveillance cameras could capture and store high-resolution video data more efficiently. It allowed the customer to expand their product line for applications ranging from home security to commercial facilities.

Upgrade and Technical Support

IMPORTANT NOTE: The total free remote technical support is limited to 60 hours. Technical support time that goes over this limit will be charged on a time and materials (T&M) basis.

Extra Engineering Notes

The JESD220A UFS 2.1 specification defines a simple but high-performance serial interface that efficiently moves data between the host processor and storage devices. The SCSI architecture model and command protocols support multiple commands with command queuing capabilities, enabling multi-threaded programming.

To achieve high energy efficiency and performance in data transmission, universal flash storage uses well-known interface standards for its interconnect layer:

- M-PHY – specification version 3.0

- UniPro – specification version 1.6

The M-PHY interface is the primary physical layer (PHY layer) for the UniPro specification and has a fast serial interface with up to 2.9 Gbps per lane (HS-G2), which can be scaled up to 5.8 Gbps per lane (HS-G3) using GTY PHY.

We can also customise our UFS IP for the LVDS PHY layer up to 1.2 Gbps per line (HS-G1) or other fast serial interfaces.

- Accelerating embedded software development

- Enhancing the existing systems through Linux BSP development

- Integrating into the various FPGA platforms and custom designs

Our FPGA Design Projects

Would you like to use our IP core for your applications and integrate UFS into your FPGA-based solution?

Drop us a line about your project! We will contact you today or the next business day. All submitted information will be kept confidential.