Ready-to-use IP Core

C37.94 Transceiver for Teleprotection Equipment

Teleprotection equipment requires high levels of reliability and fast response to ensure the smooth operation and robust protection of critical power infrastructure. At Promwad, we developed the C37.94 Transceiver IP Core, equipped with full test coverage.

This design is available for sale to companies that want to significantly reduce the time required to implement FPGA-based projects and improve the performance of industrial automation solutions, from power electronics and sensors to PdM software.

The Features of C37.94 Transceiver IP Core

- Fully compatible with the IEEE Std C37.94™-2017 standard

- Supports 1 to 12 time slots

- Master and slave modules available

- Internal clock data recovery

- Status flags

- Yellow flag

- LOS (Loss of Signal)

- YLOS (Yellow Loss of Signal); no activity control

- All-ones mode

- Headers control

- Bit error (three consecutive ones or zeroes in payload)

- Error injection for standalone IP core simulation

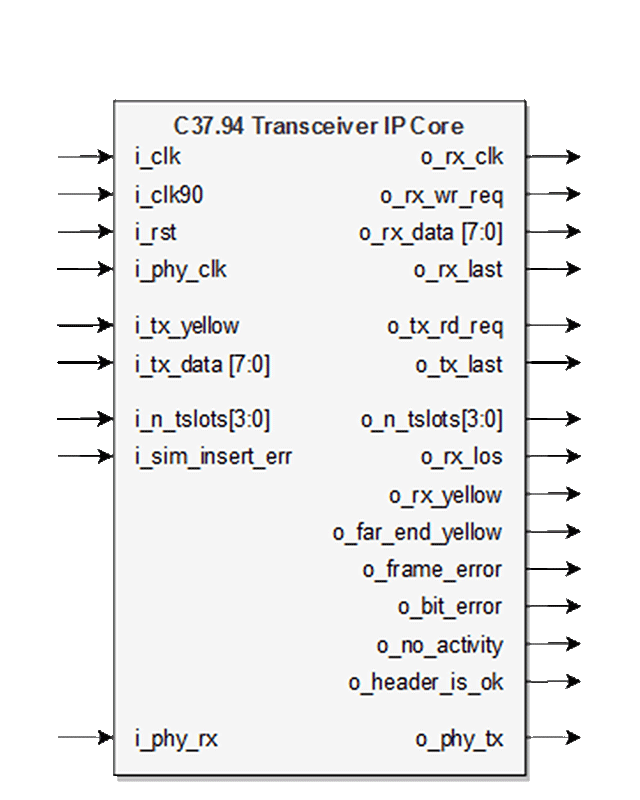

C37.94 IP core top view

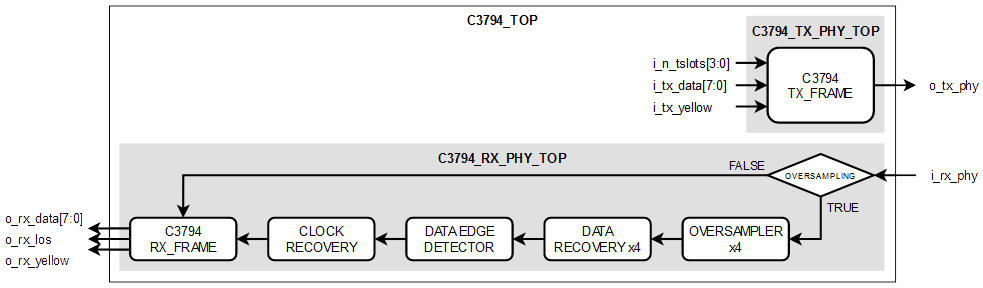

IP core C37.94 structure diagram

Deliverables: Sales Package

- Source code (VHDL)

- IP Core testbench and scripts

- Datasheet

Upgrade and Technical Support

Promwad provides free remote technical support for 1 year from your purchase date. Our offer includes consultations through phone, video calls, and email. Technical support requests will be processed within 3 business days.

IMPORTANT NOTE: The overall free remote technical support will be limited to 60 hours. All over-limit hours will be charged on a time and material (T&M) basis.

Extra Engineering Notes

C37.94 interfaces, as defined by IEEE C37.94TM-2002, transfer relay protection information between C37.94 teleprotection devices and digital multiplexers over optical fibre channels. The data frame format and rate range for the connections are standard.

These interfaces connect users' relay protection devices to the router, allowing data services for leased line connectivity to be transmitted transparently.

The most frequent channels to transmit teleprotection information are 64 kbit/s and 2 Mbit/s. On the other hand, the low transmission bandwidth of 64 kbit/s channels hinders the delivery of teleprotection information. Furthermore, when 64 kbit/s channels are employed, digital multiplexers often require 64 kbit/s codirectional interfaces that must be connected to the electric power communication networks via pulse code modulation devices. This method lengthens the signal transmission time and introduces more interference, which is critical for the development of high-precision industrial automation solutions.

Our FPGA Design Projects

Are you interested in integrating our C37.94 transceiver IP core for teleprotection into your FPGA project?

Drop us a line about your project! We will contact you today or the next business day. All submitted information will be kept confidential.