Intel Quartus Prime Design Software v21.3 with NIOS V Based on RISC-V

Earlier this month, our partner Intel released the new Quartus Prime Design Software v21.3. Intel Quartus Prime Software Suite is a design environment for Intel FPGAs, CPLD, and SoCs.

It goes in three editions: Lite, Standard, and Pro. Each of them supports different device families according to the specific design requirements. Please, explore them in the table below:

| Lite | Standard | Pro |

| Cyclone IV, V | Intel Arria 10 Arria II, V Cyclone II, V Max Series | Intel Agilex Intel Stratix 10 Intel Arria 10 Intel Cyclone 10 GX |

The new 21.3 version has several improvements and new features including:

- Performance, runtime, power, and memory improvements for the newest Intel FPGA family — Intel Agilex FPGA.

- Faster compilation option for use during the early development stages.

- Faster iterations during the debug cycle with incremental SignalTap compilation.

- Expanded visibility scope of the Signal Tap Logic Analyzer tool with Simulator Aware Signal Tap.

- And more.

What makes this version very special for Promwad?

Intel made an addition to the Nios processor series: they released the Nios V/m microcontroller. This generation of softcore processors is based on the RISC-V Instruction Set Architecture. Nios V/m is available in the Intel Quartus Prime Pro Edition Software starting only with v21.3.

The developer of free and open RISC-V is SiFive, a fabless semiconductor vendor. The curious thing is that in June, Intel announced its intentions to acquire SiFive. However, according to Bloomberg’s last week’s report, the talks broke down. The companies could not agree on financial terms.

RISC-V is a big buzz topic now. It’s catching on as a potential attempt to cheapen the technology for vendors by bringing open-source standards to chip designs. We keep watching the latest updates around the situation.

Promwad engineers have a diverse experience with the RISC-V for your FPGA & SoC design projects:

- RISC-V bootloader

- 3rd party IP core integration

- RISC-V bare-metal firmware

- Test suites development

Check out a short case-study:

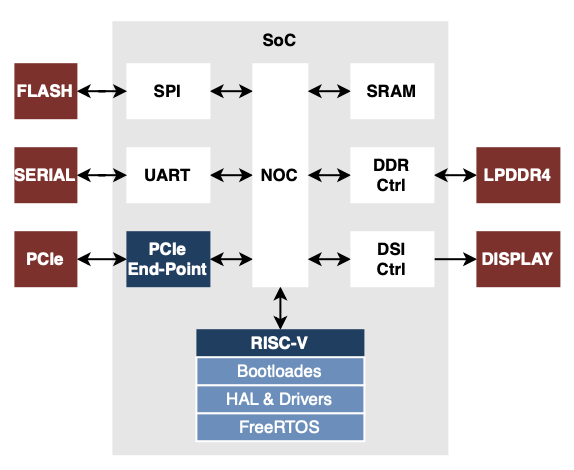

SoC firmware

RISC-V, FreeRTOS, Drivers, Bootloader

We’ve implemented firmware

for a custom-designed SoC

— RISC-V CPU

— DesignWare IPs

— Bootloaders

— IPs bare-metal drivers

— Test environment

— User software

So, we are flexible to suit both clients’ needs and the changing market of chip vendors.

Feel free to share your project ideas with us and get professional consulting and engineering services for FPGA and RISC-V! Don’t hesitate to contact us! We’ll get back to you soon.

Our projects