High-Speed Serial Interfaces in Modern Embedded Designs: PCIe, MIPI, SerDes

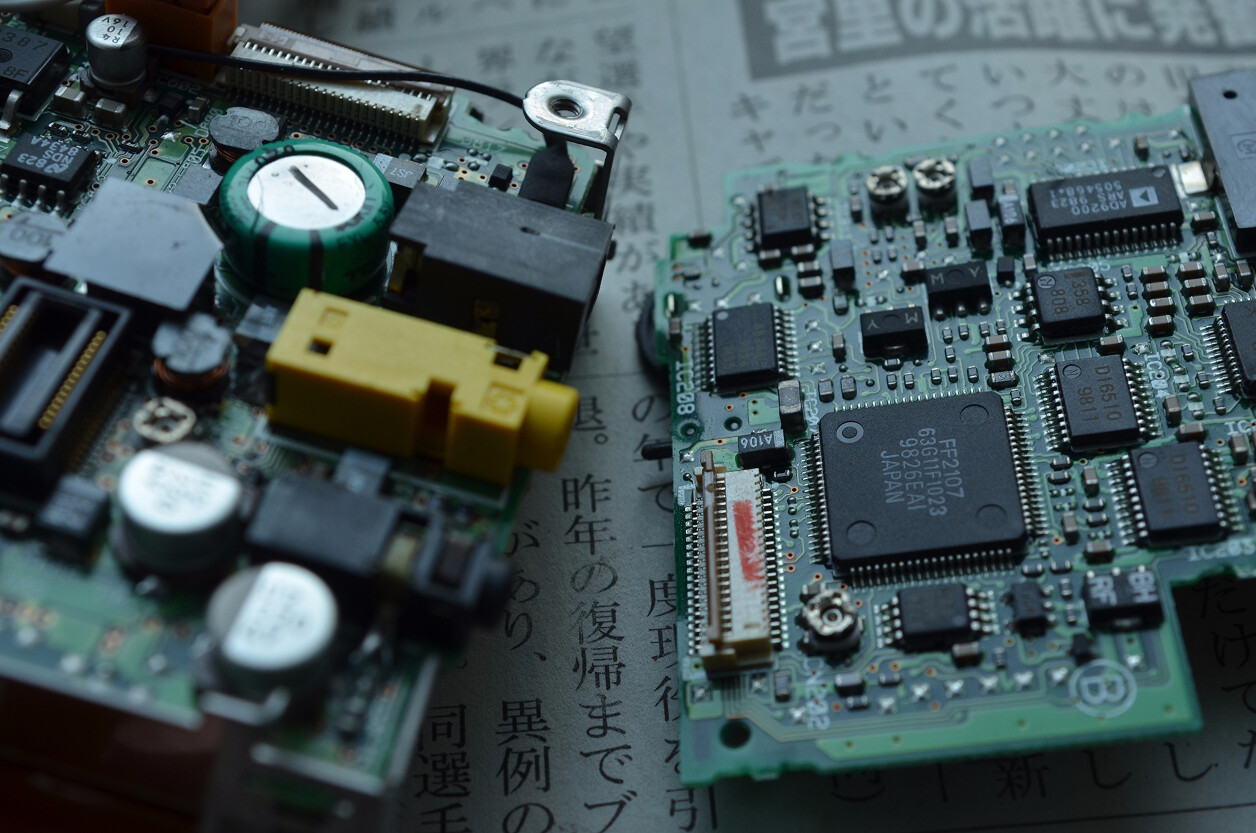

As embedded systems continue to evolve, they demand ever-higher data throughput. Whether it’s streaming 4K video in real time, transferring sensor data from cameras to SoCs, or connecting FPGAs and GPUs in compute modules, high-speed serial interfaces have become critical.

Protocols like PCI Express (PCIe), MIPI CSI/DSI, and generic SerDes lanes power modern embedded and edge devices. But these interfaces come with their own engineering complexities: signal integrity (SI), power integrity (PI), PCB stackup design, and compliance testing.

This article provides a deep dive into how these interfaces are used in embedded systems, typical design challenges, and practical tips to build robust products.

Why High-Speed Interfaces Are Taking Over Embedded Systems

Parallel buses once dominated embedded hardware. They’re simple to debug and understand. However, as frequencies climbed above 100 MHz and pin counts exploded, parallel designs ran into issues:

- Crosstalk and skew over multiple traces

- Massive connector footprints

- EMI emissions that were difficult to control

High-speed serial interfaces solve these problems by transmitting data over fewer differential pairs at very high bit rates, supported by advanced encoding and equalization. Examples include:

- PCIe Gen3+ at 8 GT/s or more per lane

- MIPI CSI-2/DSI for camera and display

- SerDes lanes reaching 25-56 Gbps in industrial FPGAs and ASICs

Typical Use Cases in Embedded Designs

PCI Express (PCIe)

- Connecting NVMe SSDs for local high-speed storage

- Linking FPGAs to CPUs or GPUs for real-time processing (e.g. AI inference accelerators)

- High-speed network interface cards (10G/25G Ethernet modules)

MIPI CSI/DSI

- CSI-2 for high-resolution cameras in robotics, drones, and automotive ADAS

- DSI driving local displays in HMIs and control panels

Generic SerDes

- FPGA transceivers connecting to optical modules or backplanes in telecom

- High-speed data acquisition boards using JESD204 for ADC/DAC connectivity

Signal Integrity (SI) Challenges in High-Speed Designs

Managing Loss and Reflection

At multi-gigabit speeds, even short PCB traces act as transmission lines. Mismatched impedances lead to reflections, which degrade eye diagrams.

Solution:

- Maintain consistent 85 or 100 Ohm differential impedance.

- Avoid stubs; keep trace lengths tightly matched within 5 mils (125 um).

- Simulate with tools like HyperLynx or Ansys SIwave.

Crosstalk

Adjacent differential pairs can couple energy, causing jitter.

Solution:

- Use spacing of at least 3x the trace width between differential pairs.

- Implement ground stitching vias along routes.

Equalization and Pre-emphasis

Modern SerDes transceivers offer adaptive equalization to recover signals. Proper tuning during bring-up is essential.

Power Integrity (PI) Considerations

High-speed SerDes drivers demand clean power rails with low ripple. Simultaneous switching of drivers (SSO) causes power fluctuations, leading to bit errors.

Tips:

- Decouple close to each driver with multi-value caps (0.01uF, 0.1uF, 1uF).

- Design low-inductance power planes.

- Consider power integrity simulation to predict resonances.

Long-Tail Questions and Practical Answers

What is SerDes in embedded systems?

SerDes stands for Serializer/Deserializer. It converts parallel data to serial form for transmission and then back. Used in FPGAs, ASICs, and SoCs to handle high-speed connections with minimal pin count.

How does PCIe differ from MIPI?

PCIe is a general-purpose, packet-based protocol used for memory-mapped IO with advanced error correction. MIPI CSI/DSI is tailored for unidirectional, low-latency streaming, ideal for cameras and displays.

What tools are used for SI analysis?

Engineers rely on HyperLynx, Altium PDN Analyzer, Keysight ADS, or Ansys SIwave to simulate impedance, losses, crosstalk, and resonance.

Can low-cost MCUs use these high-speed interfaces?

Typically no. MCUs might handle low-speed SPI/UART/I2C. High-speed interfaces require SoCs or FPGAs with dedicated PHYs and SERDES blocks.

How to design PCBs for multi-Gbps lanes?

Use differential pairs with tight length matching. Plan return paths under traces to avoid loop inductance. Implement via backdrilling or blind/buried vias to minimize stubs.

Testing and Validation

Eye Diagram Testing

Using oscilloscopes with built-in eye pattern measurement to verify signal integrity at line rate.

Bit Error Rate Testing (BERT)

Injecting known patterns and checking error rates over time. PCIe systems must pass BER thresholds like 10^-12.

Compliance and Certification

Standards bodies (PCI-SIG, MIPI Alliance) provide test specifications. Failing certification can mean costly redesigns.

Featured Case Study: Multi-stream capture where SerDes choices make or break reliability

- Sustaining throughput when many high-rate streams run in parallel (8× 4K120)

- Designing and integrating multi-gigabit links in the capture + storage path (10Gb NAS, SSDs, SAS expander)

- Signal- and power-integrity discipline to avoid intermittent bit errors at peak load

- Production readiness: OpenGear compliance, hot-swap operation, and remote monitoring/control without data loss

Future Trends: PCIe Gen5/Gen6, MIPI A-PHY

PCIe Gen5 pushes 32 GT/s per lane, demanding extremely tight SI control and advanced equalizers. MIPI A-PHY targets automotive sensor connectivity over 15+ meters of cable. New generations integrate more adaptive features in SERDES to combat channel loss.

Conclusion: Designing for High-Speed Without Surprises

High-speed serial interfaces unlock huge possibilities in embedded systems, from AI edge inferencing to real-time machine vision. But they also come with pitfalls: poorly designed boards lead to intermittent errors that only appear under temperature shifts or when all channels fire simultaneously.

Successful projects bake SI/PI analysis into the early stages, use strict layout practices, and validate with lab tools long before mass production.

At Promwad, we help clients develop complex embedded hardware that integrates PCIe, MIPI, and custom SerDes links — from schematic design and stackup planning to SI simulation and compliance testing. If you need to bring high-speed reliability into your next product, let’s discuss how we can assist.

Our Case Studies