CPE (Customer Premises Equipment) is a type of telecommunications equipment that is placed on client-site and provides user access to a public network.

Examples of CPE-devices include: telephone equipment, client-site automatic telephone exchange, auxiliary and terminal equipment, concentrators, switch-boards, routers, and other network equipment.

The primary purpose of such equipment is to provide the services of telecommunications companies, such as Internet and media providers, to end-users. The traditional Ethernet, digital xDSL line, fiber-optics GPON (Gigabit PON) channel, etc. can all function as the interface to communicate with provider network.

To manage CPE-devices on client site a remote control tool is required.

Remote device management (TR-069)

TR-069 is a technical report describing the CPE WAN management protocol. The report was published in 2004 by the DSL Forum (Broadband Forum) and is currently the most widely-used method of remote CPE configuring.

CWMP is an application layer protocol, which uses SOAP (service oriented protocol), an HTTP add-on, as an information processing tool. All information is processed in the XML format. Direct control is based on RPC (Remote Procedure Call).

To ensure secure connection the standard implies the use of standard SSL 3.0 (Secure Socket Layer) or TLS 1.0 (Transport Layer Security) protocols.

You can basically picture the TR-069 protocol hierarchy as follows:

TCP/IP → SSL/TLS → HTTP → SOAP (XML) → CWMP

The CWMP protocol is designed to implement a variety of CPE control functions, among which the following can be highlighted:

- Automatic configuring and dynamic service hookup

- Management of attachment and firmware images

- Status and productivity monitoring

- Diagnostics

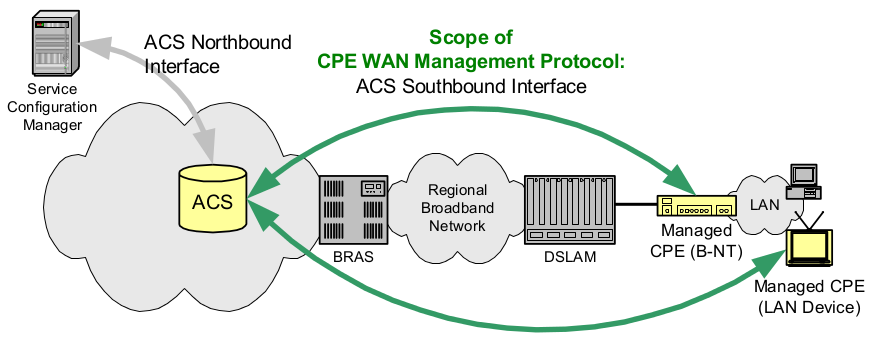

According to the report, an ACS (Auto Configuration Server) must be located at provider site, which would manage the WAN interactions, process device queries, and hook-up additional services. Management sessions may be initiated both by the CPE and, if necessary, by the ACS.

The CWMP network structure looks like this:

Structure of a managed device network with TR-069 support

The ACS server address may be specified statically, or dynamically assigned using DHCP.

TR-069 is a basic specification of the CWMP protocol; it defines the basic CPE parameters and functions. Additional fields and functions are defined by other specifications, for example TR-104 (provisioning parameters for VoIP CPE).

The TR-069 standard implies a web-interface for device management by provider operators that can implement the following functions:

- View list of devices in use

- Group devices

- View and edit parameter tree

- Update device firmware.

Broadcom processors

Broadcom offers a wide range of CPE-device processors that are price/performance optimized.

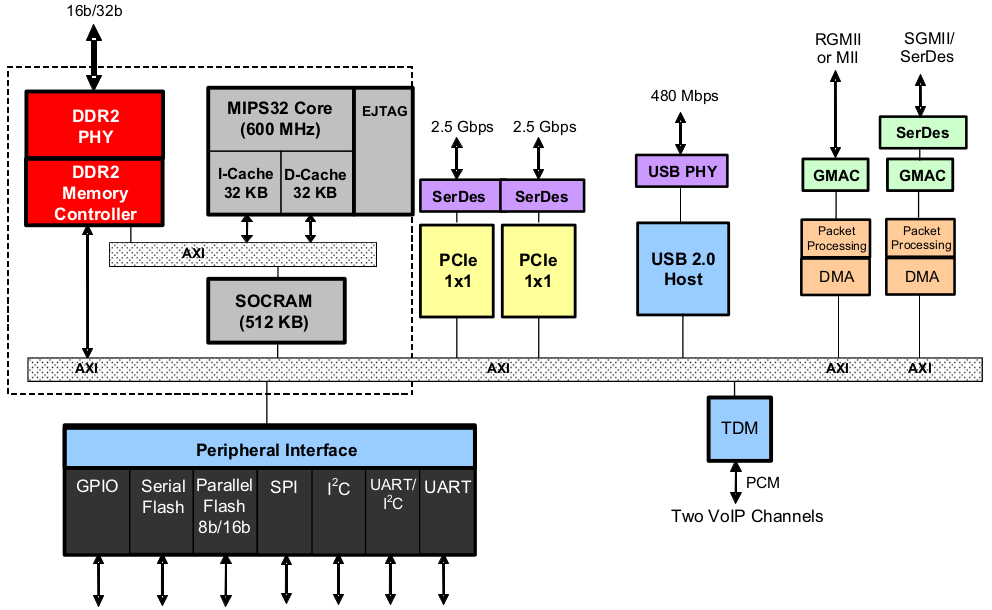

Broadcom BCM53001/BCM53003 Family

These are leading edge processors for use in various highly integrated mid- and Enterprise-level solutions. These processors are based on a 32-bit core capable of running at 600 MHz. 32-KB I-cache, 32-KB D-cache. A distinctive feature of this family is on-chip network acceleration, which reduces the CPU load.

Flow chart of the Broadcom BCM53001/BCM53003 processor family

Broadcom BCM53003 processor features:

- Processor speed up to 600 MHz

- Supports 16/32 DDR2 memory up to 333 MHz data rate

- 2 Gigabit Ethernet interfaces

- 2 PCI-Express v1.1 interfaces

- Supports USB 2.0 in host mode

- 2 full-duplex VoIP channels

Broadcom packages have been most popular in the single-chip DSL solutions area. One such processor is Broadcom BCM6362 – a highly integrated processor for use with CPE-devices. It combines a dual-core CPU with MIPS32 architecture and such peripherals as AFE (Analog Front End) ADSL2+, 802.11 support of wireless network, DECT/DECT6.0/CAT-iq for VoIP, and built-in Gigabit Ethernet switch core.

Broadcom BCM6362 features:

- Processor speed up to 400 MHz

- Dual core

- Supports ADSL2+

- Built-in switch core with 4 10/100 Ethernet interfaces and 2 Gigabit Ethernet interfaces

- 2 802.11n WLAN channels support both 2,4 GHz and 5 GHz operations

- Supports DECT/DECT6.0/CAT-iq

- Parallel expansion bus supporting CardBus and mini-PCI

- Dual USB Host/Device

- Hardware packet-processing accelerator

Marvell Kirkwood processors

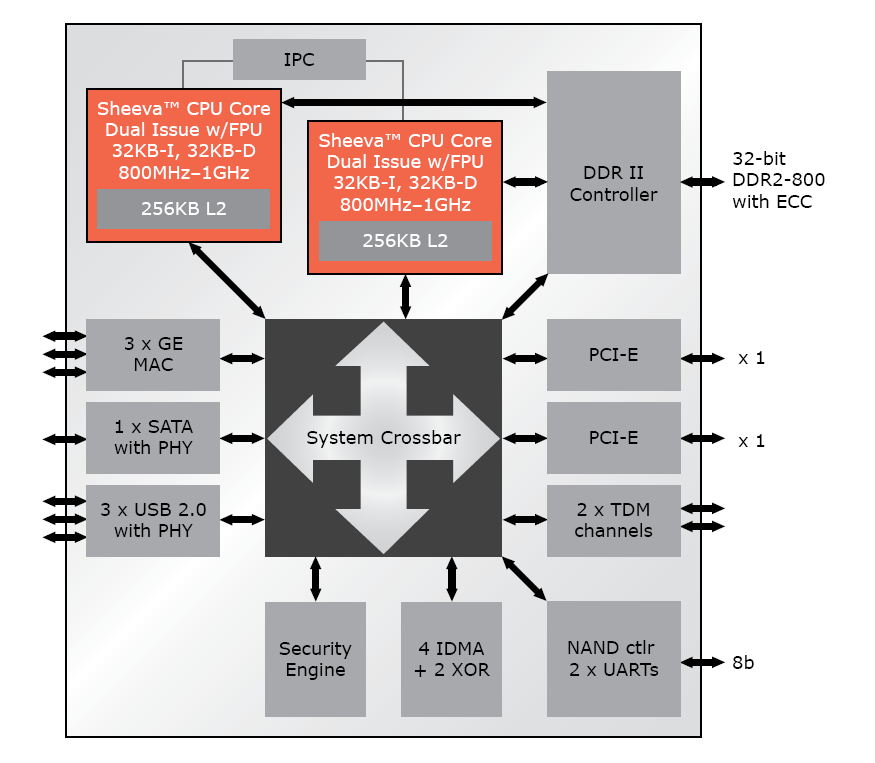

Marvell Kirkwood is a SoC (System-on-Chips) based on Sheeva ARMv5TE-compliant architecture. These processors were developed specifically for use with CPE-devices, such as navigators, access points, STB devices, network storages, media servers, and plug computers.

The Kirkwood family consists of single- and dual-core processors and a wide range of peripherals. Operating speed is 600 MHz to 2 GHz, the entire line has 256 KB L2 cache on board. The older dual-core models can boast a FPU.

Promwad is the official partner of Marvell. Details »

Let’s take a look at two processors of the Kirkwood line.

Marvell Kirkwood 88F6323 processor features:

- Dual-core

- Processor speed up to 1 GHz

- Supports 32/40 DDR2 memory up to 800 MHz data rate

- 3 Gigabit Ethernet interfaces

- 3 USB 2.0 ports

- 2 PCI-Express interfaces

- 1 SATA 2.0 port

Flow Chart of Marvell Kirkwood 88F6323

Marvell Kirkwood 88F6282 processor features:

- Single core

- Processor speed up to 2 GHz

- Supports 16-bit DDR2/3 memory up to 1066 MHz data rate

- 2 Gigabit Ethernet interfaces

- 1 USB 2.0 port

- 2 PCI-Express interfaces

- 2 SATA 2.0 ports

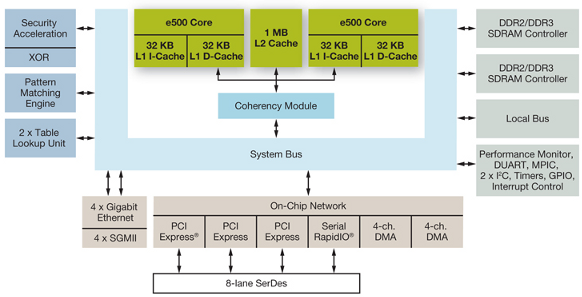

NXP processors

PowerQUICC III is the latest version of the PowerQUICC processors from NXP/Motorola, based on a 32-bit core with Power architecture, 32 KB I/D L1 cache per core and L2-cache up to 1 MB (depending on the model).

![]()

PowerQUICC III family consists of single-core (except MPC8572E) processors with clocks speeds from 533 MHz to 1.5 GHz. A built-in FPU provides double precision.

Let’s consider two processors from the PowerQUICC III line.

NXP MPC8572E processor features:

- Processor speed up to 1.5 GHz

- Dual-core

- Supports 64-bit (or 72-bit ECC) DDR2/3 memory up to 800 MHz data rate

- 4 Gigabit Ethernet interfaces

- 3 PCI-Express interfaces

Flow chart of the NXP MPC8572E processors

NXPMPC8548E processor features:

- Processor speed up to 1.5 GHz

- Single core

- Supports 64-bit DDR memory up to 200 MHz or DDR2 memory up to 266 MHz

- 4 Gigabit Ethernet interfaces

- 1 PCI-Express interface

- 1 PCI/PCI-X interface

Fast path: enhancing the performance of CPE devices

Speaking of local and global computer networks, their de facto standard is data transfer via Ethernet and TCP / IP. These protocols allow for different topologies dividing large initial networks into subnets using routers.

When transferring the information flow from Computer A to Computer B, the traffic in packets comes to the router interface eth0 which forwards the packet to the operating system where it successively passes through different levels of the TCP / IP protocol stack and is decrypted to determine the future path of the packet. After receiving the destination address and determining the redirection rules, the operating system packs the packet again, depending on the protocol used, and puts it out via the eth1 interface. Meanwhile, the bulk of the package remains unchanged and only some of the header fields change. The faster the packet goes through all these stages, the greater capacity the router can achieve. While the problem of enhancing router performance was not a big issue at the time of networks with a capacity of 100 Mbit/s, now, with the advent of gigabit speeds, there is a need to improve the efficiency of equipment.

It is easy to see that this thorough traffic processing is redundant for most packets of known types. By sifting and redirecting packets at an early stage, which are not intended for the device itself, you can greatly reduce the traffic processing time. This processing is most often performed before coming to the operating system, which reduces latencies. This technology minimizes the packet path, hence the name fastpath. Since this acceleration method is based on the low-level part of the network stack and involves information exchange with the network driver, the specific fastpath implementation technology depends on the equipment used.

Fast path technology is based on the following principles:

- Dividing of all types of network packets into frequent easily-processed ones (directed into the fast path) and the less frequent ones that require more complex processing (so-called slow path, through the network stack of the operating system).

- Ensuring maximum efficiency of identification and processing of the packets directed into the fast path.

- Reducing the size of core code in order to place it in the processor cache code.

Both hardware and software implementations of the fast path mechanism are possible.

Using fast path in packet routing enables a significant increase in efficiency. When measuring throughput of a SoC Marvell Kirkwood 88F6282-based testing device with 1 GHz processor speed using the Iperf application, the following result were obtained:

Packet type | TCP | UDP |

Packet size, byte | 1400 | 1400 |

Throughput without NFP, Mbit/sec | 281 | 338 |

Throughput with NFP, Mbit/sec | 551 | 552 |

As we see, in case of TCP traffic, the throughput almost doubles (96 per cent), which is quite noticeable. For UDP packets, the effect is not so strong. It leads to a growth of 63 per cent, but this is no bad result.

Want to implement CPE technologies in your project?

Contact us! We are ready to answer your questions.