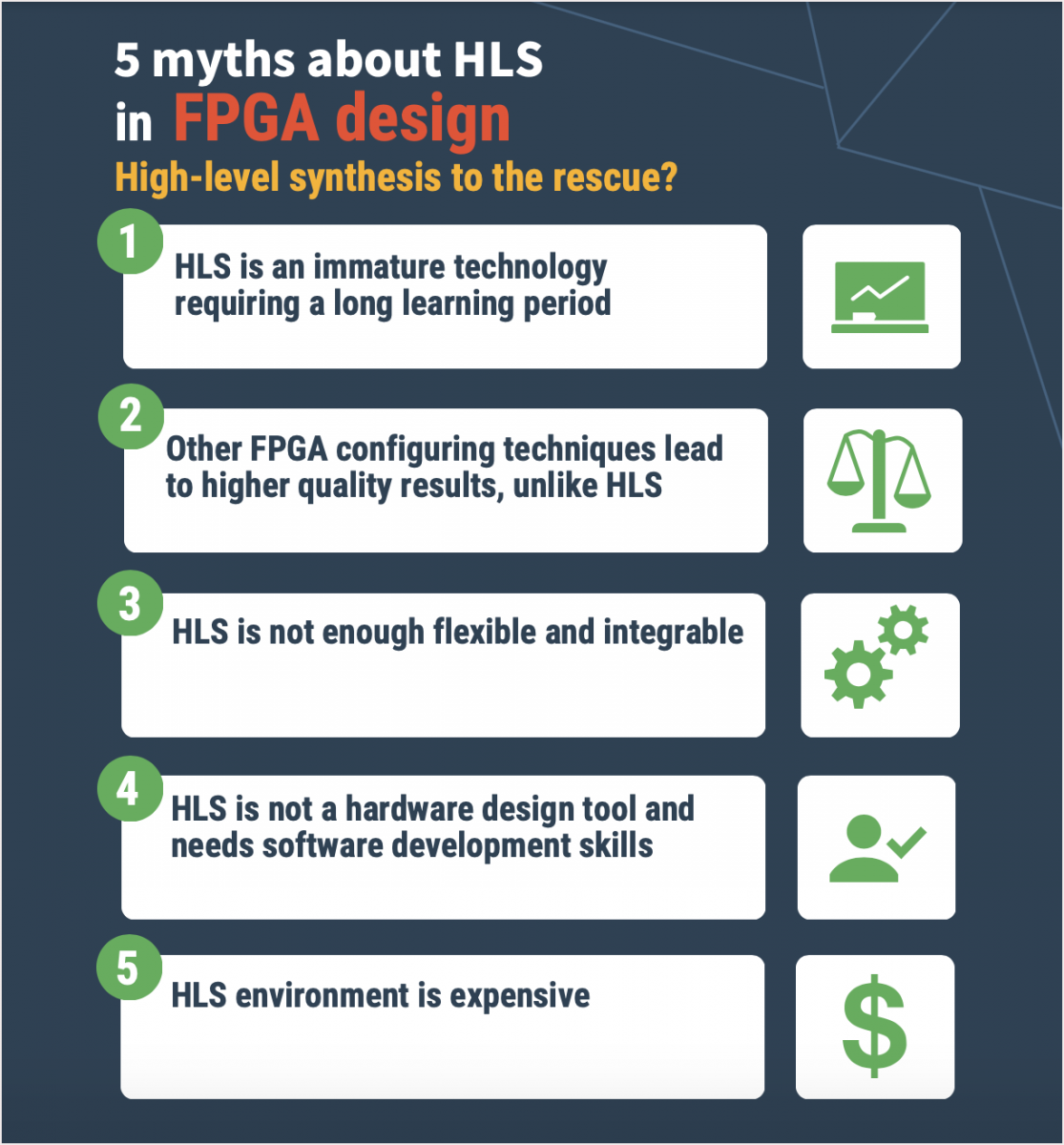

5 misbelieves about high-level synthesis in FPGA design

Although hardware description languages (HDLs) remain prevailing in FPGA programming, high-level synthesis or HLS approach is gaining momentum. Commonly used languages like Verilog or VHDL have emerged in the distant ‘80s, and both originally intended not to implement the behavior of the circuit, but to describe and simulate it. Nevertheless, most developers have resorted to these or other languages for FPGA design, until new methods and tools appeared. HLS is one of them which represents an automated programming process served to interpret the desired FPGA behavior and create hardware with this behavior. We want to dispel several myths around this concept and show how HLS helps gain value while designing systems with FPGAs.

Myth #1. HLS is an immature technology requiring a long learning period

The reason why this is a myth is that the concept itself appeared in the early 90s when Synopsys introduced their Behavioral Compiler, which though not received adequate adoption by industry players. Nevertheless, after ten years several commercially successful HLS solutions have appeared, adopted essentially in Europe and Japan, later in the US. These both cost-free and high-quality tools helped perform circuit synthesis specified at C level to a register transfer level (RTL) specification. In case you are familiar with, hence, RTL, it won’t take much time to learn the HLS approach. Today there is a huge amount of online courses developed by FPGA vendors and world-leading universities.

Myth #2. Other FPGA configuring techniques lead to higher quality results, unlike HLS

It’s fair to say that looking for VHDL engineers is like looking for a horse cab instead of a car. In case you are planning to develop a microcontroller by hand-coding, you would most probably achieve efficient results. But the question is, why not use the HLS tool and be within 15% of what you could achieve by any assembly language in most cases? Most tools distributed by vendors are greatly optimized to suit the designed product. The designer can focus more on the algorithm implementation rather than the resource and timing. So, you may reach a large gain in RTL productivity in the shortest period.

Myth #3. HLS is not enough flexible and integrable

If you decided to build your FPGA system using HLS doesn’t mean you now need to use it for the entire design. Synthesizing only complements the FPGA design-flow process. Moreover, it is better to use it in parts of the development with complex algorithms to add some inside secret elements. Vendors across the industry help to do it by providing large libraries of designs and IP. Tools contain well-documented methods and support multiple standards required by the interface.

Myth #4. HLS is not a hardware design tool and needs software development skills

Not at all. On the contrary, a software engineer would probably struggle using this approach as it requires deep hardware design experience. The reason this particular misconception exists is that you should be able to code in C/C++ or to work with SystemC or MATLAB. That is not an issue for the majority of hardware engineers.

Myth #5. HLS environment is expensive

This is another misbelief. Of course, there expensive solutions on the market, like CatapultC from Mentor Graphics and Mathworks Matlab HDL coder. Most standard software packages for hardware design include HLS tools making them available at no cost. Xilinx recently integrated the support of HLS into its Vivado toolchain at a more mainstream price point.

So, as you may see, the HLS approach could provide a significant increase in productivity. Data centers, wireless communication, vision processing, radar systems, and other embedded systems can be designed in a way more efficient.

Related articles: Promwad upgrades telecom and FPGA design projects with MATLAB & Simulink