Schematic Design for EMI/EMC Compliance: How to Prevent Failures from the First Line

Why EMI/EMC Starts at the Schematic — Not the Lab

You’ve designed a powerful, compact embedded system. The firmware is stable. The prototype boots flawlessly. But when it hits the EMC test lab… failure.

Many teams treat electromagnetic interference (EMI) and electromagnetic compatibility (EMC) as a “layout problem” or something the certification lab will help fix. In reality, most EMI issues are born at the schematic level — long before a PCB is routed.

In this article, we’ll explore best practices in schematic design that help hardware pass EMC testing on the first try.

What Is EMI/EMC — And Why It Matters

EMI (Electromagnetic Interference): Unwanted emissions that disrupt other systems

EMC (Electromagnetic Compatibility): A system’s ability to function without emitting or being affected by EMI

Regulations vary by region:

- CE / EN 55032 (EU)

- FCC Part 15 (USA)

- CISPR / MIL-STD-461 / ISO 11452 (automotive, industrial, military)

Failing EMI/EMC tests means rework, schedule slips, and increased BoM costs.

1. Define Power Domains Early

Segment your schematic into:

- High-speed digital

- RF/wireless

- Analog

- Power supply

Why it matters:

- Prevents noise coupling

- Allows for localized filtering and grounding

Assign clear names to nets and domains — even if they eventually share a plane — to guide layout and filtering.

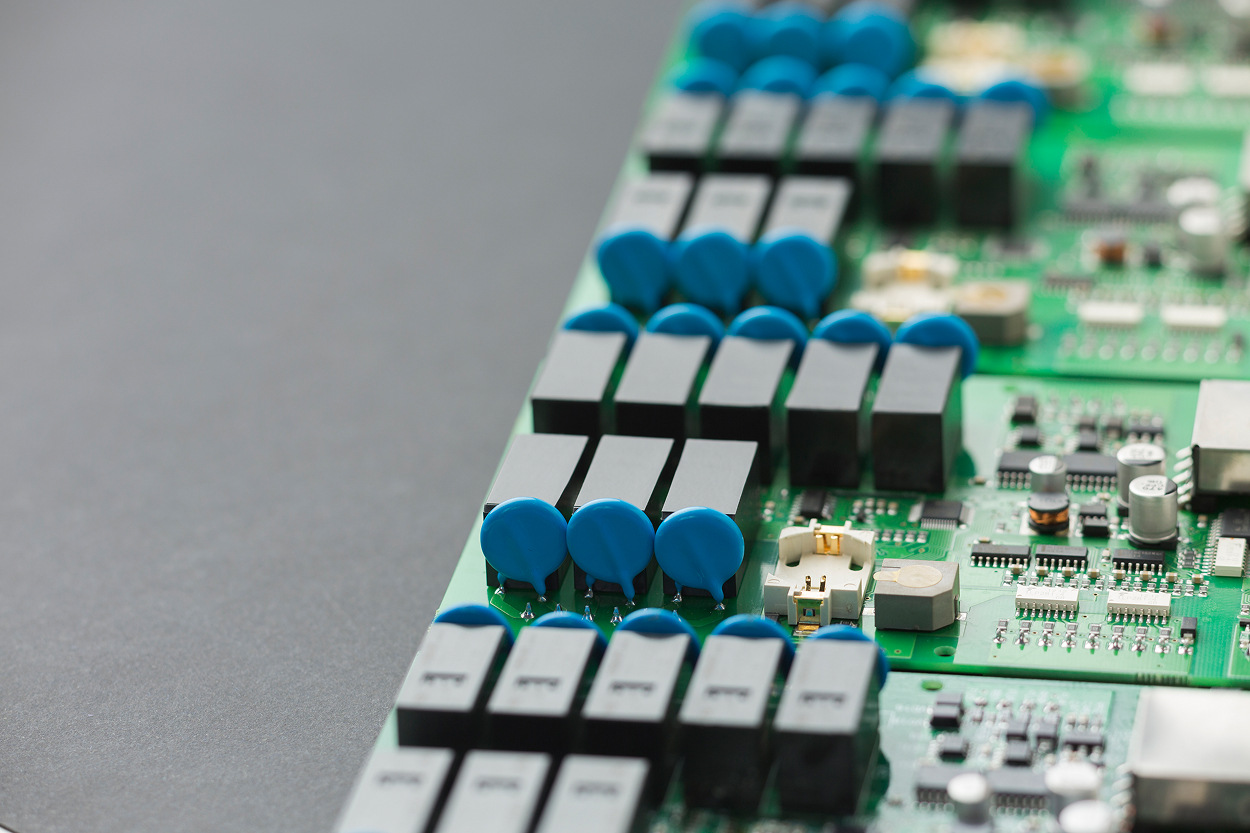

2. Add Decoupling and Bulk Capacitors the Right Way

| Capacitor Type | Use Case | Placement Rule |

| 0.01–0.1 µF | High-frequency decoupling | Closest to IC power pin (1–2 mm trace) |

| 1–10 µF (ceramic) | Mid-frequency filtering | One per power pin group |

| 10–100 µF (tantalum) | Bulk decoupling near regulators | One per power domain |

Bonus: Use separate symbols for high-speed bypass vs. bulk caps in schematics to guide PCB layout.

3. Avoid Long or Floating Digital Signal Lines

- Route unused GPIOs to known logic levels

- Avoid long trace runs from unbuffered outputs

- Use pull-ups/downs where manufacturer recommends

Why? Long floating nets act as antennas.

4. Plan for Filtering at Connectors

- Add Pi filters or ferrite beads on input power

- Consider common-mode chokes for USB, Ethernet

- Include series resistors or RC snubbers on I/O lines

Tip: Use placeholders in the schematic so you don’t forget them during layout. You can DNP later if not needed.

5. Implement Grounding Strategy in the Schematic

- Label ground types (e.g., AGND, DGND, PGND) clearly

- Avoid multiple star grounds unless required

- Define ground hierarchy — which zones connect where?

- Plan where returns will flow

Good practice:

- Analog front ends: separate AGND → connect at ADC

- Switching power: PGND separate → tie near output cap

6. Clock and Oscillator Best Practices

- Keep oscillator nets short and symmetric

- Avoid routing them near antenna lines or high-speed buses

- Buffer and shield clock sources if needed

- Don’t fan out clocks directly to distant modules via long traces — use buffers

7. Use EMI-Conscious Symbols and Notation

- Label plane layers in the notes

- Show decoupling placement zones

- Use explicit grounding connections (no implicit nets!)

Clear schematics lead to cleaner PCB and fewer surprises.

Tools and Techniques to Support EMI-Friendly Design

| Tool/Practice | Benefit |

| Signal Integrity Simulation | Identify reflection/crosstalk early |

| Power Integrity Checks | Validate decoupling strategy |

| EMC rule-driven schematics | Enforce resistor placement, net names |

| Constraint-driven layout | Bind schematic domains to layout zones |

Some modern ECAD tools (Altium, OrCAD, KiCAD + plugins) support these natively.

Common Schematic Pitfalls to Avoid

- Ground symbols everywhere with no structure

- Missing decoupling on FPGAs, MPUs, and multi-rail ICs

- Forgetting ESD protection diodes on USB/HDMI lines

- Ignoring placement constraints for switching regulators

- Using net labels but not assigning zones/domains

Final Thoughts

Electromagnetic compliance begins long before the certification lab — it starts with the schematic. Clear power domain segmentation, proper filtering, and smart grounding pay off with lower emissions, faster layout, and higher confidence at test time.

At Promwad, we apply EMI/EMC-conscious design principles from schematic through PCB layout, prototyping, and certification.

Let’s build robust, certifiable electronics — right from the start.

Our Case Studies