IP Digital Processing Core for FPGA-Based Analog Signal Filtering

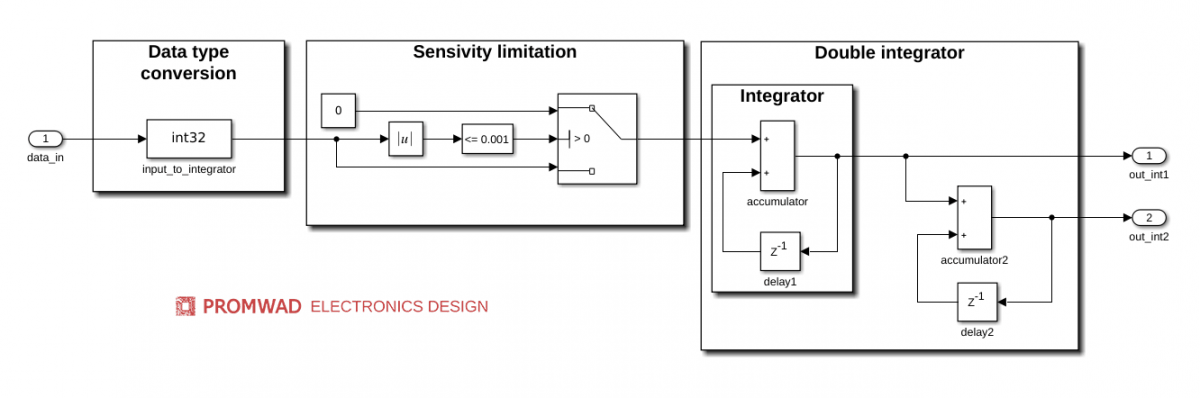

The combination of our expertise in FPGA design and substantial experience in digital signal processing has helped us to implement the IP digital processing core for filtering analog signals. The module contains a set of configurable low-pass and high-pass filters (LPF and HPF), which are built on the principle of multi-speed systems.

The key feature of this module is to provide tunable cut-off frequencies in a wide range (from fractions of Hz to hundreds of kHz) while maintaining the original sample rate. To ensure the correct operation of filters, we've implemented a signal delay via external RAM.

The project was executed using a model-based design methodology (MBD). Simulink was chosen as the software package for calculation of filter characteristics and verification of digital signal processing (DSP) module operation. The module's components RTL-code was received with the help of MATLAB and Simulink HDL Coder.

Related articles: Promwad upgrades telecom and FPGA design projects with MATLAB & Simulink

How we cut down project lifetime of a satellite modem by four times with MATLAB & Simulink

Our solutions