Broadband software-defined radio satellite modem design

Client

A European company specializing in software for the ground segment of satellite communications. It works with equipment manufacturers and providers of broadband & multimedia services.

Challenge

To design a hardware & software platform for a satellite modem. The customer decided to integrate a new hardware solution to extend its product line with the original branded solution.

Solution

We designed the device in a compact 1U form factor by dividing it into digital and analog boards. This approach helped us reach the highest flexibility: if you want to scale the device functionality, you only need to repurpose the analog frontend board.

We chose Zynq Ultrascale+ by Xilinx (AMD) as a development platform. We used the Linux OS and the programmable logic for the functionality implementation.

Our engineers have developed a dedicated front end using high-speed ADC/DAC converters and modern high-frequency analog modulators/demodulators.

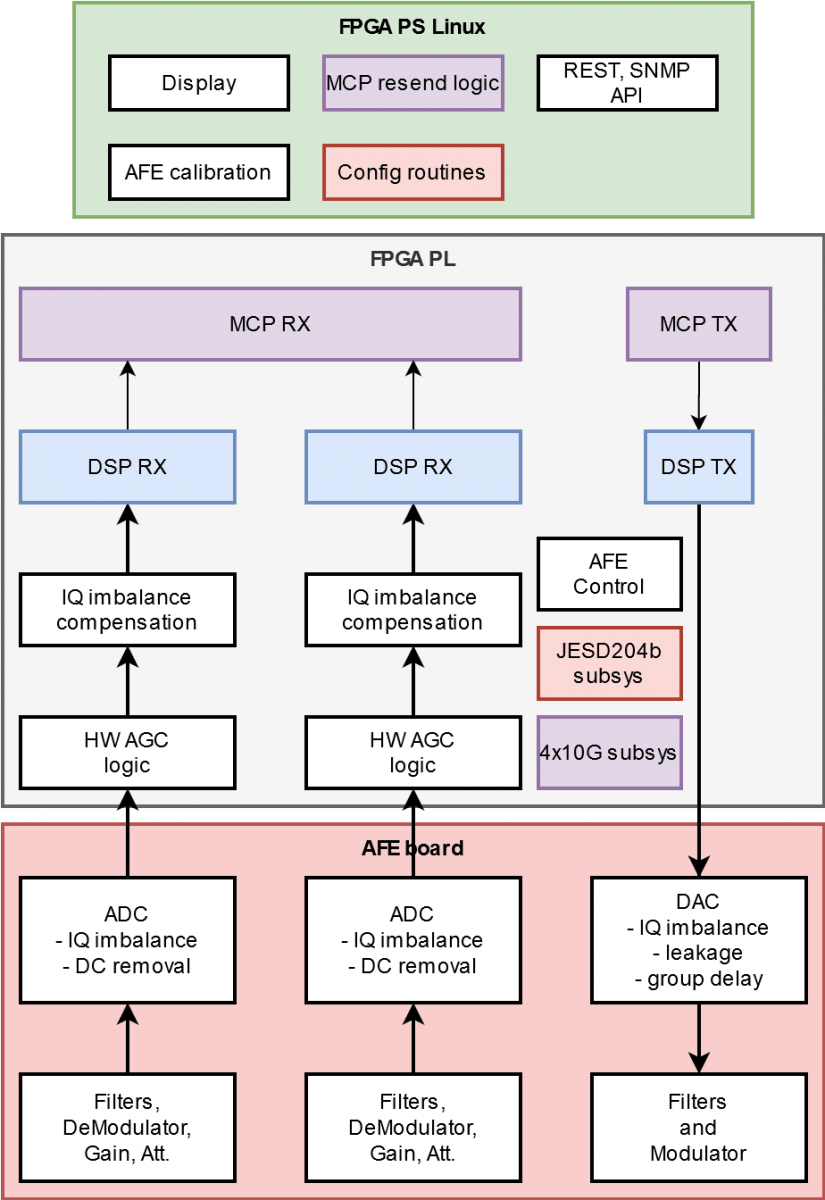

Block diagram:

We reached high-speed data exchange with a server and device with the help of four 10G interfaces and the DPDK framework. Data transmission is carried out via a specially developed MCP protocol, which ensures reliable data transmission over UDP.

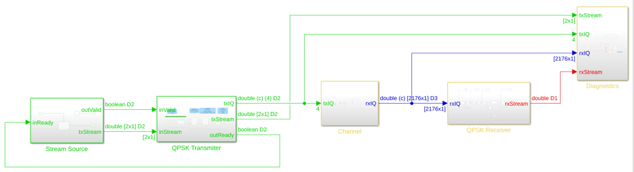

For the development of the modem and control software, we used MATLAB/Simulink.

We implemented the system model using model-based design, which means the communication system full implementation in Simulink with the subsequent HDL code generation. That resulted in the following advantages:

- Rapid design and verification.

- Processing several ADC samples per clock cycle (parallelization, unrolling, pre-calc).

- Smooth conversion to a fixed point.

- Channel model.

- BER evaluation at the design stage.

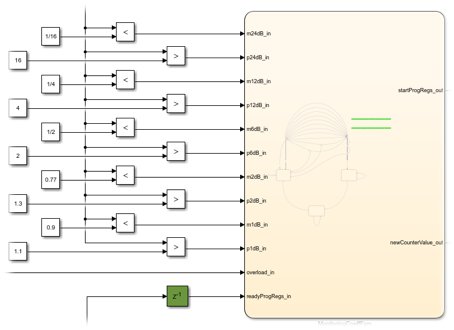

Our engineers also tested new approaches to AGC implementation and analog frontend calibration. We implemented the AGC subsystem as a Simulink model from which the HDL code was generated.

Tools used:

- Simulink State Flow

- HDL coder

- AXI4-Lite Write Master model

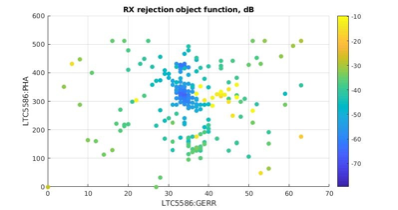

Hardware blocks in the demodulator (LTC5586), DAC (DAC37J82) and ADC (ADS54J60) compensate the following effects:

- IQ imbalance in the receiving path;

- IQ imbalance in the transmission path;

- carrier leakage;

- group delay.

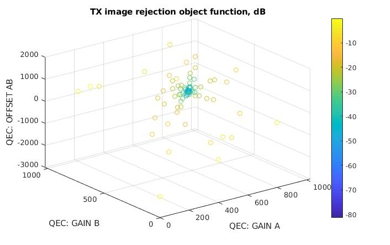

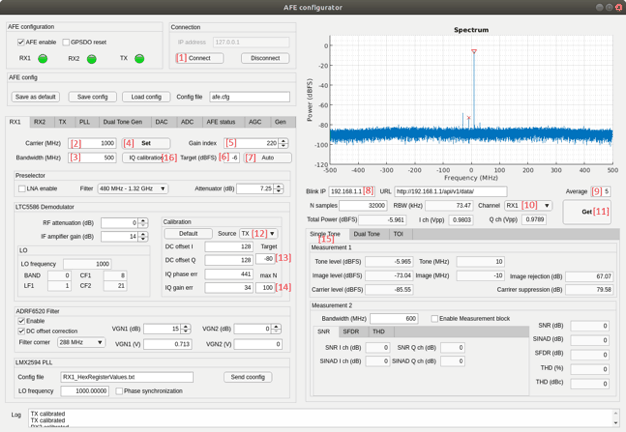

The Surrogate optimization method was used for figuring out optimal parameters in the specified operation mode. Chip registers served as parameter space. The target functions were: suppression of the mirror channel TX & RX and that one of the carrier channels.

To configure the device and measure the signal parameters, we developed a graphic application.

Business value

The customer received a satellite modem with the following features:

- frequency range: 300 MHz – 2 GHz;

- bandwidth: up to 500 MHz;

- ZERO-IF scheme;

- two receiving paths (ADC 1Gsps) and one transmitting path (1xDAC 1.5Gsps);

- 4 х 10G Ethernet for data transmission;

- Zynq Ultrascale+ platform.

Supported operating modes:

- PSK, QAM-manipulations.

- LDPC and convolutional error correction codes.