Transmission of unenscrypted data: design of hardware & software system

Client

Challenge

Solution

1. Concept Development

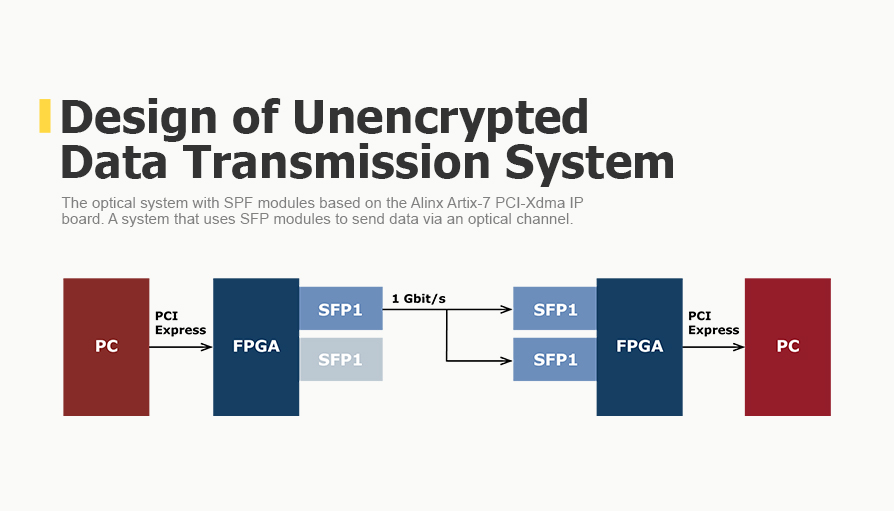

We worked out a structural diagram of the future system for transmitting/receiving unencrypted data between PCs via optical channels using SFP modules:

- On the transmission side, a continuous data stream is transferred from RAM to the SFP at 1 Gb.

- On the receiving side, two continuous data streams with a speed of 1Gb each enter the RAM from the SFP modules.

- PCI-Xdma IP x2-5Gb interacts with a PC.

- GTP IP x1-1.25Gb interacts with the SFP module.

We developed this project for the Alinx Artix-7 resource-limited PCI-Xdma IP board (XC7A35T-FGG484). To compensate the difference in frequencies and speeds between the PCI and GTP interfaces, and taking into account the available resources of the board, we developed three options:

- Using multiple FIFO buffers and queuing logic for continuous transmission/reception of a data stream.

- Using one large FIFO buffer without queuing logic for continuous transmitting/receiving data streams.

- Using DDR memory for continuous transmitting/receiving a data stream.

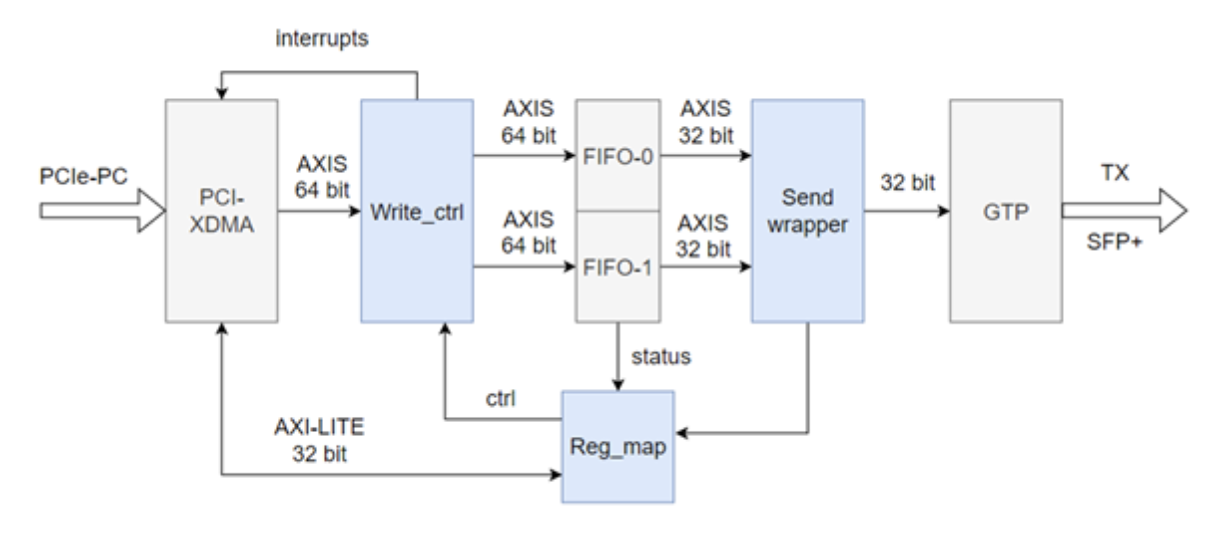

We chose the first option to implement the project and used two FIFO buffers of 32768 bytes.

2. Software Development

The transfer process is controlled via the register map. The Write_Ctrl module receives the data stream from PCI-XDMA and writes it to FIFO-0. When FIFO-0 is full, the Write_Ctrl module writes data to FIFO-1. Then the process is repeated.

When FIFO-0 is full, the Send_wrapper module reads and transmits the data stream to GTP IP. When FIFO-0 is empty, Send_wrapper reads data from FIFO-1 and transmits it to GTP IP. Then the process is repeated. If no data is transferred in the buffer, then an interrupt is set.

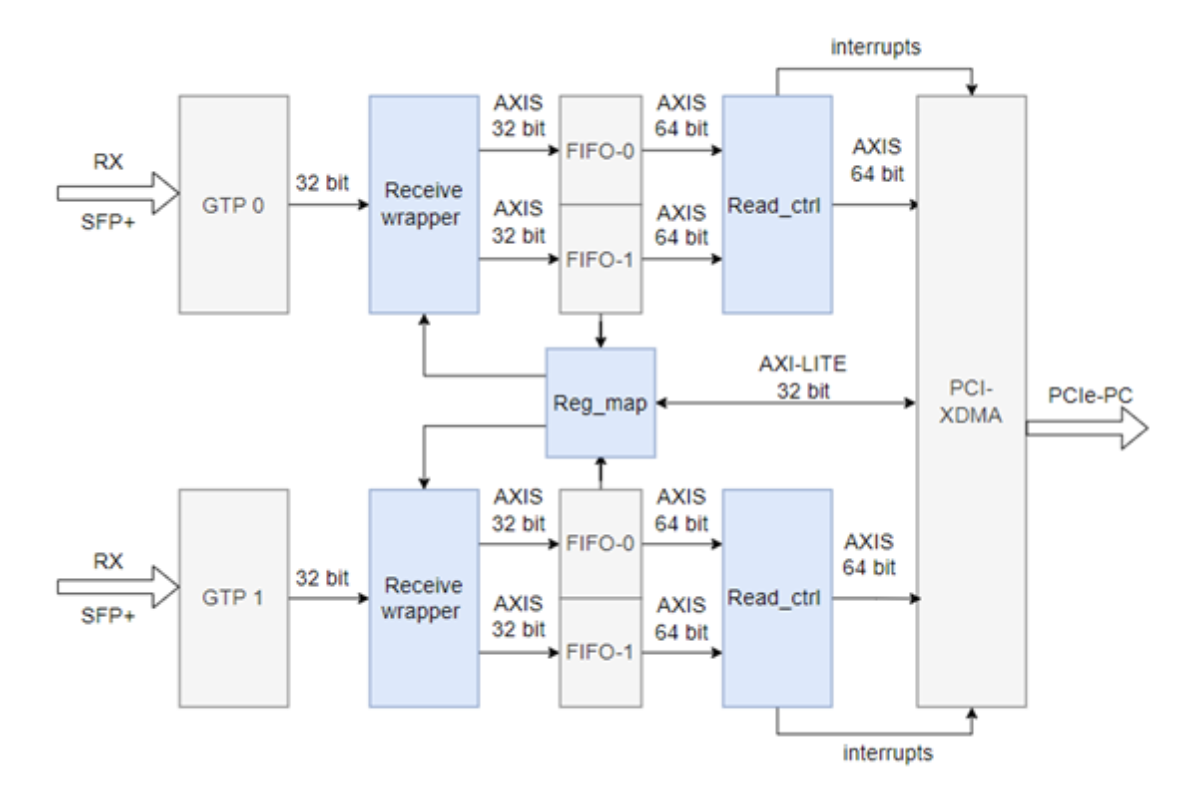

On the receiving side, we used a two-channel Xilinx PCI-Xdma IP x2-5Gb to interact with a PC and a two-channel Xilinx GTP IP x2-1.25 Gb to interact with two SFP modules. Both channels (0 and 1) are independent.

To compensate for the difference in frequencies and speeds in each channel, we use two FIFO buffers of 16384 bytes each. The transfer process from each channel is controlled via the register map.

The Receive_wrapper module receives the data stream from the SFP-GTP and writes it to FIFO-0. When FIFO-0 is full, the Receive_wrapper module writes data to FIFO-1. Then the process is repeated. If there is no free space in the buffers for new data during the test, an interrupt is set.

When FIFO-0 is full, the Read_ctrl module starts reading and transmitting the data stream to PCI-XDMA. When FIFO-0 is empty, Read_ctrl reads data from FIFO-1 and transmits it to PCI-XDMA. Then the process is repeated.

Business Value

We created a system that uses SFP modules to send data via an optical channel. This system provides a reliable and efficient means of transmitting data over long distances, which is essential for businesses operating in dispersed locations. The use of SFP modules in the system would make it highly scalable, allowing companies to expand their operations and increase their capacity.